### Evaluación de la calidad de TRAM en la detección de fallas de fabricación en circuitos integrados analógicos fabricados en tecnología CMOS de 500nm

# Sebastián Pazos<sup>1</sup>, Fernando Aguirre<sup>1</sup>, Tomás Mazur<sup>1</sup>, Gabriela Peretti<sup>2</sup>, Eduardo Romero<sup>2</sup>

- <sup>1</sup> Universidad Tecnológica Nacional, Facultad Regional Buenos Aires, Av. Medrano 951, (C1179AAQ) Ciudad Autónoma de Buenos Aires, Argentina

- <sup>2</sup> Universidad Tecnológica Nacional, Facultad Regional Villa María, Av. Universidad 450, (5900) Villa María, Córdoba, Argentina

spazos@frba.utn.edu.ar

Recibido el 15 de diciembre de 2014, aprobado el 21 de enero de 2015

#### Resumen

En este trabajo se presenta la evaluación de la capacidad de la estrategia de test denominada Método de Análisis Transitorio (TRAM, Transient Analysis Method) para la detección de fallas paramétricas en los componentes pasivos de un filtro activo de segundo orden. Se pretende realizar evaluaciones similares a las previamente reportadas pero con modelos de simulación considerablemente más exactos y que responden a una tecnología específica. Con este propósito, se ha diseñado un filtro en una tecnología CMOS de 500nm y se lo ha adoptado como caso de estudio. Los modelos de simulación a nivel transistor han sido empleados en las evaluaciones. Nuestros resultados confirman los problemas de la estrategia para la detección de desviaciones paramétricas pequeñas.

**PALABRAS CLAVE:** METODO DEL ANÁLISIS DE LA RESPUESTA TRANSITORIA – TRAM – FILTRO DE SEGUNDO ORDEN – TESTING DE CIRCUITO INTEGRADOS ANALÓGICOS

### **Abstract**

This work presents the evaluation of the ability of the so called Transient Analysis Method (TRAM) for detecting parametric faults in the passive components of a second-order active filter. We perform evaluation similar to the previously reported but using a considerably more detailed simulation model. A particular technology is targeted for the filter design. Particularly a 500nm CMOS technology has been proposed and the resulting filter adopted as case study. Transistor-level simulation model has been used for our evaluations. Our results confirm the problems of TRAM for detecting small deviation in the components.

**KEYWORDS:** TRANSIENT RESPONSE ANALYSIS METHOD - 2ND ORDER FILTERS - ANALOG IC TESTING

### Introducción

Las metodologías de test de productos electrónicos pueden definirse como el conjunto de procedimientos aplicados durante el proceso de fabricación de dichos productos y orientados a la detección y descarte de los sistemas o componentes que no cumplan con las especificaciones. Los procedimientos de test permiten la consecución de diferentes objetivos, entre los que deben mencionarse los siguientes: evitar que un producto defectuoso llegue al usuario, reducir los costos de fabricación al evitar pasos de procesamiento sobre un producto defectuoso, la generación de datos sobre la marcha del proceso de producción y la clasificación de productos según su desempeño.

En la actualidad, el test de circuitos analógicos y de señal mixta impacta severamente en el costo de los mismos, superando valores del 33% dependiendo de las características particulares del circuito bajo test. En particular, las secciones arriba mencionadas ocupan por lo general áreas de silicio pequeñas comparadas con sus contrapartes digitales. Sin embargo, presentan los problemas más desafiantes. Esto se debe a la naturaleza de las señales involucradas y a la baja observabilidad de los nodos internos de los circuitos.

Lo señalado, junto con la necesidad de reducir los costos de producción ha motivado que las comunidades académicas e industriales dedicaran grandes esfuerzos al desarrollo de metodologías de test para circuitos analógicos y de señales mixtas (Vinnakota, 1998; Chatterjee et al, 1997). Una particular atención han recibido los filtros, debido a que son ampliamente utilizados en una multiplicidad de aplicaciones.

Una de las alternativas para el test de filtros es el enfoque funcional, que propone medir las especificaciones del circuito y determinar si se encuentran dentro de una ventana de aceptabilidad. Normalmente, la aplicación de este enfoque consume mucho tiempo y es muy costoso. Frente a ello se generaron diferentes alternativas para el test de estos circuitos, basadas en algún tipo de reconfiguración y el agregado de circuitos (Soma, 1990; Vázquez et al, 1994; Romero et al, 2005).

Entre estos métodos se destaca por su simplicidad conceptual y de aplicación el Método de Análisis Transitorio (TRAM, *Transient Analysis Method*), aplicable a filtros de segundo orden (Calvano et al, 1999, 2000, 2005). Este método se basa en excitar el circuito bajo test con un estímulo que provoque un transitorio subamortiguado, asumiéndose que una falla provocará la alteración de algunos de los parámetros de su respuesta transitoria. El monitoreo de estos parámetros permitirá la detección de las fallas.

Los trabajos mencionados anteriormente han establecido la eficiencia de TRAM introduciendo fallas que no tienen en cuenta la variabilidad estadística de los parámetros del circuito. En los trabajos de Peralta et al (2007, 2009, 2011), se tienen en cuenta estas variaciones y se evalúa la estrategia desde las visiones comportamental y estructural. Sin embargo, la misma se realiza mediante el uso de ecuaciones que caracterizan el transitorio y que suponen comportamiento ideal de todos los componentes del circuito. En este trabajo se realiza un estudio más profundo, orientado a una tecnología de fabricación específica, que tiene en cuenta el comportamiento no ideal de todos los componentes. En particular, se evalúa la capacidad de TRAM para la detección de fallas paramétricas en los componentes pasivos del circuito bajo test utilizando un modelo de simulación mucho más detallado que en los trabajos previos.

### TRAM: Conceptos y filtro bajo prueba

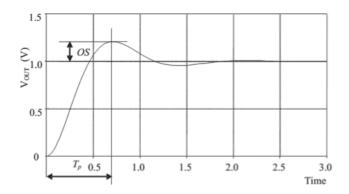

TRAM es una metodología de test para filtros de segundo orden que propone el monitoreo de parámetros característicos de una respuesta subamortiguada a un estímulo determinado. Este estímulo puede ser una señal escalón, rampa o parábola dependiendo de las características del filtro (pasa-bajos, pasaaltos, etc.). Es esperable que una falla en los componentes del filtro resulte en desviaciones de dichos parámetros. Usualmente, el tiempo al pico (Tp) y la sobre-elongación relativa (%OS) son evaluados (Calvano et al, 1999, 2000). Un filtro determinado es declarado defectuoso si estos parámetros presentan valores por fuera de los límites preestablecidos. Tp y OS pueden identificarse en la Figura 1, que representa la respuesta transitoria típica de un filtro de segundo orden pasa-bajos a

Fig. 1. Respuesta subamortiguada típica de un sistema de segundo orden

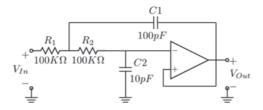

Fig. 2. Filtro activo pasa-bajos de topología Sallen-Key

una señal escalón. Estos parámetros guardan una relación directa con los parámetros característicos de la respuesta en frecuencia del filtro, conocidos como parámetros directos (Calvano et al, 1999), a saber el factor de selectividad Q, la frecuencia de polo  $\omega_0$  y el coeficiente de amortiguamiento  $\zeta$  obtenido como 1/2Q (Ogata; 2002).

## Respuesta subamortiguada típica de un sistema de segundo orden

La topología Sallen-Key mostrada en la Figura 2 es ampliamente utilizada para implementar filtros de segundo orden. Sus parámetros funcionales  $(Q, \omega_0 y \zeta)$  dependen del valor de los componentes pasivos del circuito según (1-3), y las características de la respuesta temporal pueden ser calculadas a partir de estos parámetros mediante las expresiones (4) y (5). Cabe destacar que (1) a (5) han sido obtenidas considerando al amplificador operacional como ideal.

Filtro activo pasa-bajos de topología Sallen-Key

$$\omega_0 = \frac{1}{\sqrt{R_1 R_2 C_1 C_2}} \tag{1}$$

$$Q = \sqrt{\frac{C_1 R_1 R_2}{C_2} \frac{1}{R_1 + R_2}} \tag{2}$$

$$\xi = \sqrt{\frac{C_2}{4C_1R_1R_2}}(R_1 + R_2) \tag{3}$$

$$OS = e^{-\pi \left(\frac{\xi}{\sqrt{1-\xi^2}}\right)} \cdot 100\% \tag{4}$$

$$T_p = \pi / \left(\omega_n \sqrt{1 - \xi^2}\right) \tag{5}$$

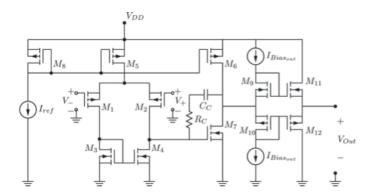

## Diseño del amplificador operacional y transferencia del filtro

Para implementar el filtro bajo prueba, se diseñó un amplificador operacional (Op Amp) en una tecnología CMOS de 500nm. Para reducir la resistencia de salida del mismo y aumentar la capacidad de corriente, se agregó una etapa de salida *push-pull* complementaria en configuración seguidor de fuente (source follower). En la Figura 3 puede verse el circuito esquemático a nivel transistor del amplificador diseñado, donde las etapas diferencial y de ganancia esta compuestas por los transistores M1 a M7, compensadas mediante la red Rc-Cc, y la etapa *push-pull* de salida conformada por los transistores M9 a M12.

Fig. 3. Circuito esquemático del amplificador operacional diseñado para sintetizar los filtros

| Parámetro                  | Valor              |  |  |  |

|----------------------------|--------------------|--|--|--|

| $Av_0$                     | 100 dB             |  |  |  |

| GBP                        | 2,018 MHz          |  |  |  |

| Rout (Lazo Abierto)        | 800 Ω              |  |  |  |

| SR+/SR- (Small Signal)     | 0,9 / -0,75 μV/sec |  |  |  |

| Output Swing (Vmin / Vmax) | -1,06 / 1,39 V     |  |  |  |

Tabla 1. Resultados de la Caracterización del OpAmp

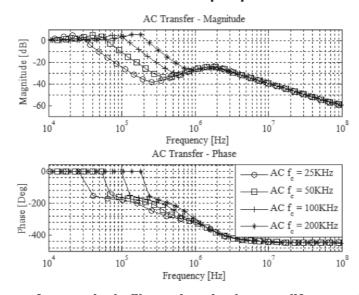

Fig. 4. Respuesta en frecuencia de filtros sintetizados con diferentes frecuencias de corte

La referencia de corriente es una referencia de VT (Tensión Térmica) de 10 uA. Se realizaron simulaciones exhaustivas para caracterizar el circuito diseñado, obteniéndose los resultados que constan en la Tabla 1.

La Figura 4 representa la respuesta en frecuencia de 4 filtros diseñados con la misma topología, en magnitud y fase, paradistintas frecuencias de corte. Puede apreciarse la influencia de los ceros en alta frecuencia que resultan de la resistencia de salida no nula del amplificador real. Para frecuencias de corte elevadas, estas no idealidades introducen desviaciones en los valores esperados de los parámetros del filtro y, más importante para este trabajo aún, las fallas paramétricas influyen en forma diferente sobre los paráme-

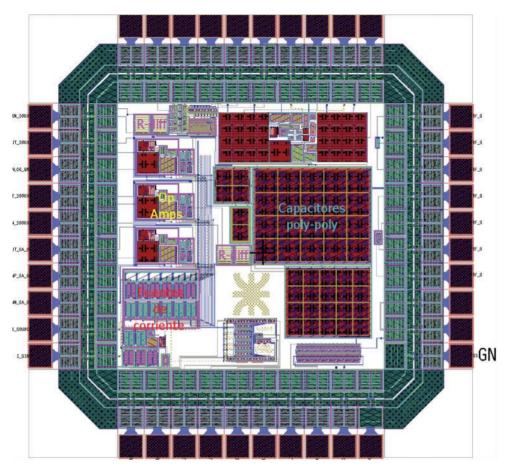

Fig. 5. Vista de layout del circuito integrado con distintos filtros sintetizados

tros de test para cada caso, a tal punto que se requieren diferentes métodos estadísticos para el estudio de la estrategia de *testing*. Para este trabajo, un filtro pasa-bajos de frecuencia de corte 50KHz fue elegido como filtro bajo prueba para la evaluación de TRAM, puesto que presenta influencias virtualmente nulas debido a las no idealidades del amplificador y los valores de los componentes son lógicos desde la viabilidad de la integración en la tecnología de fabricación bajo estudio (considerando el gran área de silicio requerido para integrar capacitores y resistores).

El filtro sintetizado fue diseñado para ser integrado y enviado a fabricar en un chip de 1,5mm x 1,5mm de área, con el objetivo de obtener mediciones a futuro sobre el comportamiento del mismo para contrastar con los límites obtenidos durante la evaluación de la calidad de TRAM. El layout del circuito integrado puede apreciarse en la Figura 5, donde se destacan los capacitores integrados como los componentes más demandantes en lo que respecta a área de silicio requerida.

### Procedimiento de evaluación de la calidad de TRAM

# Parámetros de test (TPs) y Límites de Tolerancia Estadísticos (LTE)

Para poder evaluar la capacidad de TRAM de detectar fallas paramétricas, es necesario, en primera instancia, determinar el rango de valores que los parámetros de test (Tp y %OS en este trabajo) pueden adoptar debido a variaciones estadísticas inherentes al proceso de fabricación. Para este fin, se implementaron simulaciones de Monte Carlo de 5000 corridas en SPICE, teniendo en cuenta las bandas de tolerancia relativas (al valor nominal del componente) especificadas por el fabricante para los componentes integrados: 37% en distribución normal a 3 $\sigma$  (3 desvíos estándar) para los resistores difundidos en N-well, y 11% en distribución normal a 3<sub>o</sub> para los capacitores coplanarios poly-poly. Para cada corrida de Monte Carlo, se relevó la respuesta temporal del filtro ante una excitación escalón, con un valor pseudo-aleatorio para cada componente

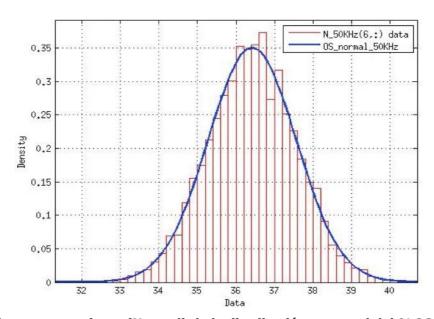

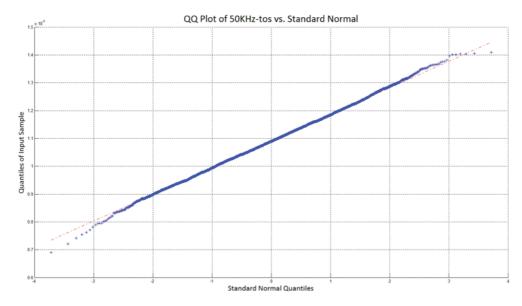

Fig. 6. Histograma y ajuste (Normal) de la distribución muestral del %OS

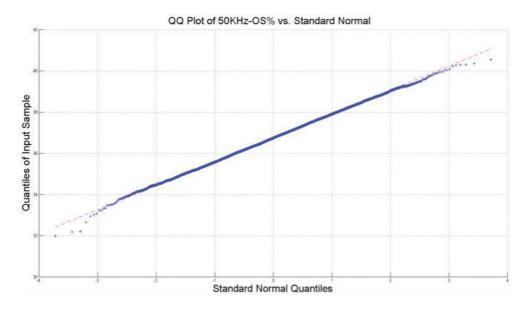

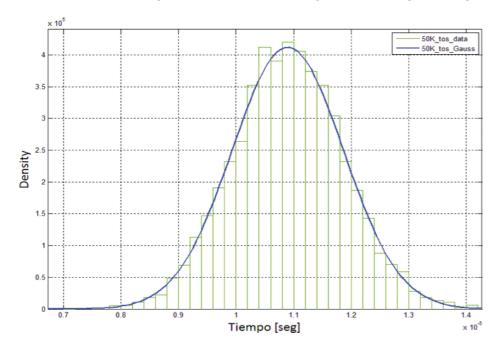

considerando la distribución especificada, y se obtuvo el valor de los TPs. Sobre el espacio muestral obtenido se realizó un Análisis Exploratorio de Datos y se emplearon test de normalidad para verificar que los TPs siguen una distribución Normal. Algunas de las herramientas utilizadas con este fin son las gráficas cuantil-cuantil (Q-Q), los histogramas y los test de normalidad.

La Figura 6 es el histograma de la distribución resultante de las muestras tomadas para el %OS, mientras que la Figura 7 es la gráfica Q-Q del mismo parámetro para filtro bajo prueba. El estudio visual de los histogramas no suele ser suficiente para inferir sobre la distribución de la población, pero su utilización conjunta con las gráficas Q-Q permite plantear una primera hipótesis de normalidad para el espacio muestral. Estas gráficas comparan cómo se distribuyen los cuantiles de la muestra baio estudio con los cuantiles de una distribución normal (recta discontinua en las gráficas). Cuanto la distribución de los cuartiles más se asemeja a la recta normal, se puede inferir con mayor seguridad una distribución normal para la población bajo estudio. Para los parámetros analizados, se pueden apreciar pequeños sesgos (asimetrías, apreciables por los desvíos de los cuartiles hacia arriba y abajo en los extremos de la recta) o las llamadas "colas pesadas" (mayor probabilidad de valores lejanos a la media). Sin

embargo, no presentan desviaciones apreciables, lo cual es verificado posteriormente de forma analítica.

La verificación analítica de normalidad se realizó mediante 3 tests de bondad de ajuste: Anderson-Darling, Jarque-Bera y Lilliefors, que hacen hincapié en distintas características de la distribución normal a la hora de inferir normalidad de una muestra, como ser su sesgo, curtuosidad o influencia de muestras muy lejanas a la media (outliers) (Montgomery, 2003). Los resultados de estos tests pueden apreciarse en la Tabla 2 para el %OS, en la que se hallan los p-valores resultantes del test (p) que se utilizan como elemento de decisión, el valor del estadístico k de prueba calculado para cada test y el valor crítico de este estadístico que resultaría en un rechazo de la hipótesis nula. Del mismo modo, para el parámetro Tp, los resultados se muestran en las Figuras 8 y 9 y en la Tabla 3. Los resultados indican que no se puede rechazar, con un 95% de certeza, la hipótesis nula de que la población de valores de los TPs analizados se ajusta a una distribución normal.

Con esta inferencia verificada, para una muestra que puede considerarse de distribución Normal, los LTE superior e inferior (USTL y LSTL de sus siglas en inglés) pueden ser calculados mediante (6) y (7), donde N es el tamaño de la muestra, p es la proporción

Fig. 7. Curva Q-Q de los datos muestrales del %OS

| TEST             | Decisión | h [1=Fail] | р      | k      | С      |

|------------------|----------|------------|--------|--------|--------|

| Anderson-Darling | p >0.05  | 0          | 0.6479 | 0.2859 | 0.7518 |

| Jarque-Bera      | p >0.05  | 0          | 0.4502 | 1.5464 | 5.9810 |

| Lilliefors       | p >0.05  | 0          | 0.5000 | 0.0076 | 0.0128 |

Tabla 2. Resultados de las pruebas de bondad de ajuste Normal para el %OS

| TEST             | Decisión | h [1=Fail] | р      | K      | С      |

|------------------|----------|------------|--------|--------|--------|

| Anderson-Darling | p >0.05  | 0          | 0.3350 | 0.4164 | 0.7518 |

| Jarque-Bera      | p >0.05  | 0          | 0.1129 | 4.3283 | 5.9810 |

| Lilliefors       | p >0.05  | 0          | 0.2886 | 0.0099 | 0.0128 |

Tabla 3. Resultados de las pruebas de bondad de ajuste Normal para el Tp

Fig. 8. Histograma y ajuste (Normal) de la distribución muestral del Tp

Fig. 9. Curva Q-Q de los datos muestrales del Tp

de la población normalmente distribuida que será contenida dentro de los LTE calculados y  $\gamma$  (gamma) la confianza de esta asunción según la distribución Chi-Cuadrado. Para el presente trabajo, se estableció que el 99% de la población esté contenida entre los límites de tolerancia con un 95% de confianza. En la Tabla 4 se detallan los valores obtenidos para los LTE para las muestras evaluadas de cada parámetro.

$$LSTL = \bar{X} - k_2 \sigma \qquad USTL = \bar{X} + k_2 \sigma$$

(6)

$$k_2 = \sqrt{\frac{(N-1)\left(1+\frac{1}{N}\right)z_{(1-p)/2}^2}{\chi_{1-\gamma,v}^2}}$$

$$con \quad v = (N-1) \tag{7}$$

Modelo de falla y procedimiento de inyección de fallas El objetivo de este trabajo es evaluar, con un modelo de simulación más realista que los previamente utilizados, la capacidad de TRAM para detectar fallas paramétricas en los componentes pasivos del filtro. Para este fin, es necesaria la adopción de un modelo de fallas.

Se adoptó el modelo utilizado por Sunter (1999) y Liu (2000), que considera que solo un componente puede presentar fallas mientras todos los demás adoptan valores aleatorios dentro de las tolerancias del proceso de fabricación (Saab, 2000), aseguradas por el proveedor de la tecnología. La falla es introducida asignando al componente fallado un valor determinístico por encima o por debajo de su valor nominal esperado. Puntualmente, para este estudio se evaluaron desviaciones desde un 10% hasta un 50% por encima y por debajo del valor nominal del componente diseñado.

Para cada falla inyectada, los TPs son nuevamente evaluados mediante campañas intensivas de simulación de Monte Carlo, y compa-

| Parámetro      | LSTL      | USTL       |

|----------------|-----------|------------|

| T <sub>p</sub> | 8.36 µsec | 13.40 µsec |

| %OS            | 33.723 %  | 39.743 %   |

Tabla 4. LTE Superior (USTL) e Inferior (LSTL) del proceso

rados, en cada corrida, con los LTE obtenidos previamente. Si al menos un TP presenta un valor por fuera de los límites calculados, la falla es considerada como detectada. La Probabilidad de Detección de Falla (FDP de sus siglas en inglés) puede definirse como en (8), donde NDF es el número de fallas detectadas y NIF el número total de fallas inyectadas. Es esperable una mejora en la FDP si se evalúa más de un TP al mismo tiempo, pero debe considerarse la relación de compromiso entre el costo de test asociado al monitoreo de diversos TPs al mismo tiempo y el incremento de la FDP.

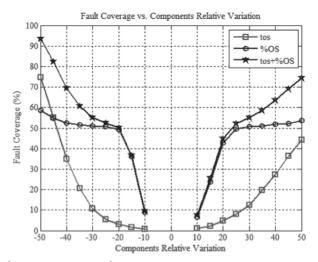

La FDP es una métrica muy específica para cada componente evaluado. En cambio la Cobertura de Fallas (FC) otorga una mejor visión de la calidad del método, y puede ser calculada mediante (9) (Khouas, 2000), que representa un promedio donde m es la cantidad de componentes considerado en el análisis, *i* representa para cada componente y *j* el valor de la desviación relativa en su valor. Este promedio permite determinar una caracterización más general de la calidad de la estrategia de test.

$$FDP = \frac{NDF}{NIF} \tag{8}$$

$$FC\%_{j} = \frac{\sum_{i} FDP_{ij}}{m} \tag{9}$$

### Resultados de la inyección de fallas

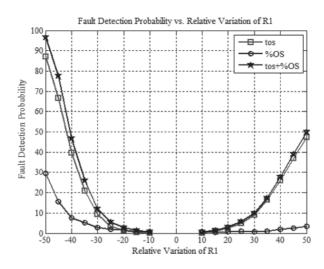

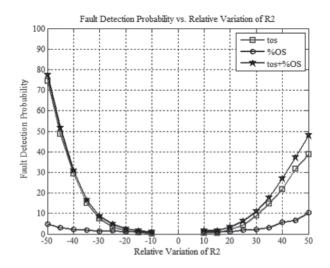

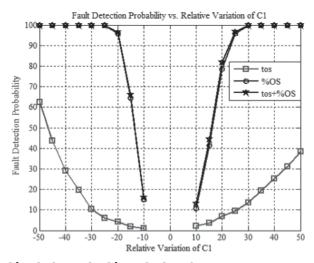

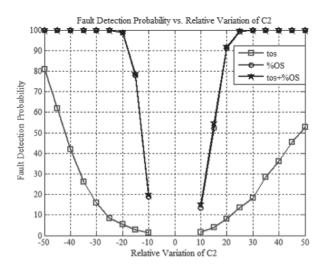

De la Figura 10 a la Figura 13 se observan las FDP para cada componente y TP bajo análisis. La Tabla 5 junto con la Figura 14 muestra la FC considerando un promediado de los resultados de todos los componentes involucrados. El signo "+" representa la evaluación conjunta de ambos TPs, considerando una falla como detectadas toda vez que uno de ellos adopta un valor por fuera de los LTE (suma lógica, OR) (Mitra, 1998).

Estos resultados y, particularmente la representación de los mismos, permiten tomar decisiones de compromiso en el intercambio entre costo y tiempo de test y la cobertura de fallas del mismo. Puede verse que para resistores o capacitores únicamente, considerar ampos TPs no provee un incremento considerable en la FDP, pero al analizar la cobertura general para el circuito bajo estudio considerando todos los componentes, se obtienen valores considerablemente mayores en la FC, especialmente para desviaciones por debajo del 30%. Cabe destacar que, en el caso de los resistores, la alta incertidumbre en la resistencia por cuadrado debida al proceso de fabricación atentan contra la calidad del test en la detección de las fallas, mientras que para los capacitores, variaciones relativamente pequeñas pueden ser detectadas sólo con monitorear el %OS.

Fig. 10. FDP en función de la variación relativa de R1

Fig. 11. FDP en función de la variación relativa de R2

Fig. 12. FDP en función de la variación relativa de C1

Fig. 13.FDP en función de la variación relativa de C2

Fig. 14. FC en función de la variación relativa de los 4 componentes, para dos TPs

| TPs                  | Variación relativa de los componentes |      |      |      |      |      |       |      |      |

|----------------------|---------------------------------------|------|------|------|------|------|-------|------|------|

|                      | <i>50%</i>                            | 45%  | 40%  | 35%  | 30%  | 25%  | 20%   | 15%  | 10%  |

| Тр                   | 44.3                                  | 36.2 | 27.0 | 19.7 | 12.5 | 8.0  | 4.9   | 2.3  | 1.1  |

| %OS                  | 53.5                                  | 52.3 | 51.9 | 51.0 | 50.7 | 49.5 | 42.84 | 23.8 | 6.5  |

| T <sub>p</sub> + %OS | 74.5                                  | 69.1 | 63.7 | 58.7 | 55.2 | 52.1 | 45.0  | 25.4 | 7.6  |

| TDe                  | Variación relativa de los componentes |      |      |      |      |      |       |      |      |

| TPs                  | -10%                                  | -15% | -20% | -25% | -30% | -35% | -40%  | -45% | -50% |

| Тр                   | 0.7                                   | 1.5  | 3.1  | 5.3  | 10.8 | 20.5 | 35    | 55.3 | 74.6 |

| %OS                  | 8.8                                   | 36.1 | 49.2 | 50.8 | 51.1 | 51.7 | 52.5  | 54.7 | 58.6 |

| Tp + %OS             | 9.42                                  | 36.8 | 50.1 | 52.5 | 55.2 | 60.6 | 69.4  | 82.3 | 93.5 |

Tabla 5. Cobertura de fallas (FC%) considerando todos los componentes para distintas variaciones respecto del valor nominal

#### **Conclusiones**

En este trabajo se presenta la evaluación de la capacidad de TRAM para la detección de fallas paramétricas en un filtro de segundo orden. El objetivo de este trabajo ha sido la determinación más precisa de esta capacidad, mediante modelos de simulación más exactos que los utilizados en trabajos previamente reportados. Para este propósito se diseñó un filtro en tecnología CMOS de 500nm con un enfoque totalmente a medida (full custom) y se lo adoptó como caso de estudio. Se utilizaron los modelos de simulación SPI-CE a nivel transistor para los procedimientos de inyección y simulación de fallas. Esto marca una diferencia considerable con los trabajos previos que consideraban fallas paramétricas pero utilizaban simulaciones a nivel de ecuaciones.

Nuestros resultados de simulación han evidenciado (confirmando resultados previos en el nivel comportamiento) los problemas que presenta esta estrategia para la detección de fallas para-

métricas pequeñas. Estos resultados sugieren la necesidad de monitorear otros parámetros de la respuesta transitoria para intentar mejorar tanto la FDP como la FC.

A futuro se profundizarán los estudios, incluyendo fallas en los transistores del amplificador operacional (catastróficas y de desviación) y se ampliará la evaluación incluyendo otros atributos de test.

### **Agradecimientos**

Los autores agradecen a Silvio Tapino, Patricio Fernández Canto y Basilio Robino (UTN-FRBA) por las discusiones inspiradoras mantenidas durante el desarrollo del presente trabajo. La investigación que dio lugar a estos resultados recibió financiamiento por parte de la Universidad Tecnológica Nacional, Facultad Regional Buenos Aires a través del Proyecto de Investigación y Desarrollo número UTN2166, dirigido por Sebastián Verrastro (UTN-FRBA).

### Referencias

CALVANO, J.; ALVES, V. y LUBASZEWSKI, M., (1999) "Fault detection methodology for second order filters using compact test vectors transient analysis", en Proceedings of the 3rd International Workshop on Design of Mixed-Mode Integrated Circuits and Applications, pp. 1824, Puerto Vallarta, Mexico.

CALVANO, J.; ALVES, V.y LUBASZEWSKI, M., (2000) "Fault detection methodology and BIST method for 2nd order Butterworth, Chebyshev and Bessel filter approximations", en Proceedings of the 18th IEEE VLSI Test Symposium (VTS '00), pp. 319-324.

CALVANO, J.; MESQUITA FILHO, A.; ALVES, V. y LUBASZEWSKI, M., (2001) "Faults Models and Test Generation for Op Amp-the FFM", J. Electron. Test: Theory Appl, Vol. 27, pp. 121-138.

CHATTERJEE, A. y NAGI, N., (1997) "Design for testability and built.in self-test of mixed-signal circuits", in Proceedings of the 10th International Conference on VLSI Design, pp. 388-392.

KHOUAS, A. y DERIEUX, A., (2000) "Fault Simulation for Analog Circuits Under Parameter Variations". Journal of Electronic Testing: Theory and Applications Vol. 16, pp. 269-278.

LIU, F. y OZEV, S., (2007) "Statistical Test Development for Analog Circuits under High Process Variations", IEEE Trans. Comput. Aided Des. Integr. Circuits Syst., Vol. 26, pp. 1465-1477.

MITRA, A., (1998) Fundamentals of Quality Control and Improvement. Upper Saddler River, New Jersey, US: Prentice Hall, 2nd. Edition.

MONTGOMERY, D. C. y RUNGER, G. C., (2003) "Applied Statistics and Probability for Engineers". New York, US: John Wiley & Sons, Inc., 3ra. Edición.

OGATA, K., (2002) Modern Control Engineering, 4ta. Edición, New York: Prentice Hall.

PERALTA, J.; PERETTI, G. y ROMERO, E., (2007) "Evaluación del Análisis de Respuesta Transitoria Bajo Condición de Falla Paramétrica". Actas XIII Taller Iberchip.

PERALTA, J.; PERETTI, G. y ROMERO, E., (2007) "Capacidad del Test Basado en Análisis de Transitorio para Detectar Fallas Paramétricas". Ingeniare. Revista chilena de ingeniería, Vol. 15 Nº 2, pp. 124-131.

PERALTA, J.; PERETTI, G.; ROMERO, E. y MARQUÉS, C., (2009) "A new performance characterization of transient analysis method", International Journal of Electrical and Information Engineering, vol. 3, pp. 251-258.

SUNTER, S. y NAGI, N., (1999) "Test Metrics for Analog Parametric Faults", in Proceedings of the 17th. VLSI Test Symposium, pp. 226-234.

SAAB, K.; BEN-HAMIDA, N. y KAMINSKA, B., (2000) "Parametric fault simulation and test vector generation". Proceedings of the Conference on Design, Automation and Test in Europe pp. 650-657. SOMA, M., (1990) "A design-for-test methodology for active analog filters", in Proceedings of the IEEE International Test Conference, pp. 183-192.

VAZQUEZ, D.; RUEDA, A. y HUERTAS, J., (1994) "A new strategy for testing analog filters", in Proceedings of the 12th. VLSI Test Symposium, pp. 36-41.

VINNAKOTA, B., (1998) "Analog and Mixed-Signal Test", Prentice Hall, New York, United States.