# **TESIS DE DOCTORADO**

Mención procesamiento señales e imágenes

"Desarrollo de un sistema de adquisición adhoc para el control y medición remota de magnitudes físicas en vehículos no tripulados"

Autor: Ing. Adrián G. Stacul

Director de Tesis: Dr. Ing. Mario B. Lavorato

Co-Director de Tesis: Ing. Daniel A. Pastafiglia

Buenos Aires – 2019

| "Es curios |                      |                      |                     | cto con la gente que piens<br>n lo mismo que pienso yo |  |

|------------|----------------------|----------------------|---------------------|--------------------------------------------------------|--|

|            | - 10 CONTRAINA AQ 11 | o awe vo nienso, aw  | e ae ios aue niensa | n to mismo aue bienso vo                               |  |

|            | io comitanto de n    | o que yo pienso, qu  | e de los que prensa |                                                        |  |

|            | io comitanto de la   | o que yo premio, qu  | e de 105 que piensa | Salvador Dal                                           |  |

|            | io comitanto de la   | o que jo premio, qu  | e de los que piensa |                                                        |  |

|            | io comitanto de la   | o que jo premio, qu  | e de 105 que piensa |                                                        |  |

|            | io comitanto de la   | g que jo premio, qu  | e de los que piensa |                                                        |  |

|            |                      | g que jo premio, qu  | e de los que piensa |                                                        |  |

|            |                      | g que jo premio, qu  | e de los que piensa |                                                        |  |

|            |                      | g que jo premio, qu  | e de los que piensa |                                                        |  |

|            |                      | g que jo premio, qu  | e de los que piensa |                                                        |  |

|            |                      | s que jo premio, qui | e de los que piensa |                                                        |  |

|            |                      | o que jo premo, qu   | e de los que piensa |                                                        |  |

|            |                      | o que jo premo, qu   | e de los que piensa |                                                        |  |

#### **AGRADECIMIENTOS**

Si bien, aún estoy corrigiendo las ultimas cuestiones sobre esta tesis, me he tomado el tiempo de distraerme un rato y escribir estos párrafos y pensar en cada una de las personas que estuvo a mi lado ayudándome en este camino.

La lista es extensa, ya que muchas personas han colaborado de manera directa e indirecta con esta escritura, y desde hace varios años. Sin duda las primeras personas que me gustaría agradecer es a mi director Mario y mi codirector Daniel, ya que han luchado (y siguen) por muchas cuestiones políticas que han sucedido en el instituto en estos últimos años, y me han animado a seguir adelante tanto en buenos momentos como en tiempos difíciles.

También quiero agradecer a Edgardo Comas, Sergio Saluzzi, Martín Morales, Sebastián Alvarez, Gerardo García y Ariel Dalmas Di Giovanni que conviven conmigo en CITEDEF, de los que aprendo día a día y me han tenido una especial paciencia y atención.

Por último y no por ello menos importantes, quiero agradecer su apoyo y comprensión a: mi pareja, a mis padres, a mis amigos de toda la vida, y al resto de toda mi familia.

# TABLA DE CONTENIDOS

| Agradecimiento    | os                                         | iii  |

|-------------------|--------------------------------------------|------|

| Tabla de conter   | nidos                                      | vi   |

| Lista de ilustrac | ciones                                     | ix   |

| Lista de tablas.  |                                            | xiii |

| INTRODUCCI        | IÓN                                        | 1    |

| Antecedentes      | s y fundamentos                            | 1    |

| Justificación     | del problema                               | 2    |

| Estado del ar     | te                                         | 5    |

| Objetivos         |                                            | 6    |

| Metodología       |                                            | 7    |

| CAPITULO 1 -      | - SISTEMAS DE TELEMETRÍA                   | 9    |

| 1.1. Descri       | ipción general de un sistema de telemetría | 9    |

| 1.2. Hardw        | vare de a bordo                            | 12   |

| 1.2.1. Sens       | sores                                      | 12   |

| 1.2.2. Mod        | lulación                                   | 13   |

| 1.2.3. Com        | mutación                                   | 16   |

| 1.2.4. Patro      | ones de sincronización de datos            | 17   |

| 1.3. Puesto       | o de tierra                                | 18   |

| 1.3.1. R          | econstrucción de la trama PCM              | 18   |

| 1.3.2. Si         | incronización de tramas                    | 20   |

| 1.3.3. D          | De-conmutación                             | 22   |

| 1.3.4. S          | imulación y codificación                   | 23   |

| 1.3.5. Pi         | rocesamiento en tiempo real                | 23   |

| 1.3.6. G          | Graficadores de tiempo real                | 23   |

| 1.3.7. G          | Sestión de archivos                        | 23   |

| 1.3.8. D          | Pistribución de datos                      | 23   |

| 14 Fin de         | el capítulo                                | 24   |

| CAPÍTULO 2 - TECNOLOGÍA FPGA                            | 26 |

|---------------------------------------------------------|----|

| 2.1. Conceptos fundamentales                            | 27 |

| 2.1.1 PLA                                               | 28 |

| 2.1.2. PAL                                              | 30 |

| 2.1.3. CPLD                                             | 32 |

| 2.1.4. FPGA                                             | 32 |

| 2.2. Arquitectura de los dispositivos FPGA              | 33 |

| 2.2.1. Bloques lógicos configurables                    | 34 |

| 2.2.2. Bloques de entrada/salida                        | 35 |

| 2.2.3. Interconexiones                                  | 36 |

| 2.3. Formas de desarrollo e implementación              | 37 |

| 2.3.1. Lenguaje esquemático                             | 37 |

| 2.3.2. Lenguajes de descripción de hardware             | 38 |

| 2.3.3. Suite de desarrollo ISE                          | 41 |

| 2.3.4. Flujo de implementación para ISE                 | 43 |

| 2.3.5. Librería System Generator para FPGAs Xilinx      | 44 |

| 2.4. Placas de desarrollo Xilinx                        | 48 |

| 2.4.1. Atlys                                            | 48 |

| 2.4.2. 3PX1                                             | 50 |

| 2.4.3. Análisis comparativo entre las tarjetas Xilinx   | 51 |

| 2.5. Fin del capítulo                                   | 52 |

| CAPITULO 3 – DISEÑO Y DESARROLLO DEL SISTEMA ADQUISIDOR | 54 |

| 3.1. Simulador PCM                                      | 57 |

| 3.1.1. Características Generales                        | 58 |

| 3.1.2. Ventajas y limitaciones                          | 59 |

| 3.1.3. Bloques fundamentales                            | 60 |

| 3.1.3.1. Enable Generator                               |    |

| 3.1.3.2. Clock Generator                                | 63 |

| 3.1.3.3. Buffer                                 | 64  |

|-------------------------------------------------|-----|

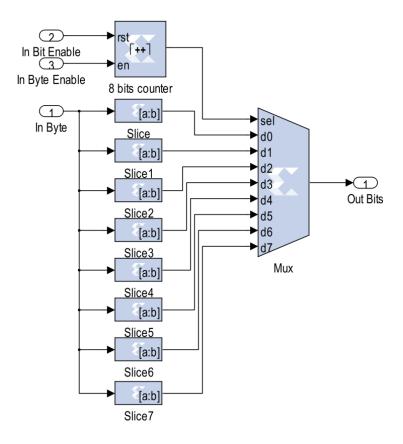

| 3.1.3.4. Byte to Bits                           | 65  |

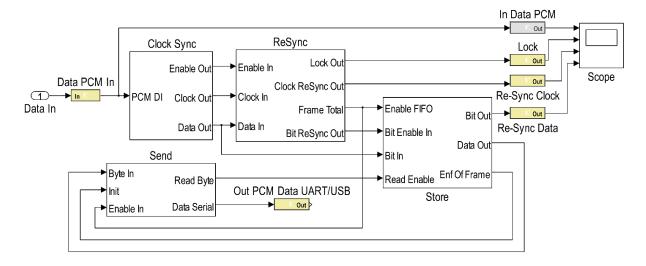

| 3.2. Adquisidor PCM                             | 66  |

| 3.2.1. Ventajas y limitaciones                  | 68  |

| 3.2.2. Bloques fundamentales                    | 69  |

| 3.2.2.1. Clock Sync                             | 70  |

| 3.2.2.2. ReSync                                 | 71  |

| 3.2.2.3. Store                                  | 72  |

| 3.2.2.4. Send                                   | 74  |

| 3.3. Ensayos en hardware                        | 78  |

| 3.4. Implementación del filtro digital para PCM | 82  |

| 3.4.1. Filtro PCM                               | 84  |

| 3.4.2. Teoria del filtro CIC                    | 84  |

| 3.4.3. Implementación del filtro CIC            | 87  |

| 3.5. Verificaciones del sistema                 | 91  |

| 3.6. Resultados                                 | 97  |

| CONCLUSIONES                                    | 109 |

| BIBLIOGRAFÍA                                    | 115 |

| ANEXOS                                          | 118 |

| 4.1. Formato de Trama PCM                       | 118 |

| 4.2. Configuración de la FPGA                   | 120 |

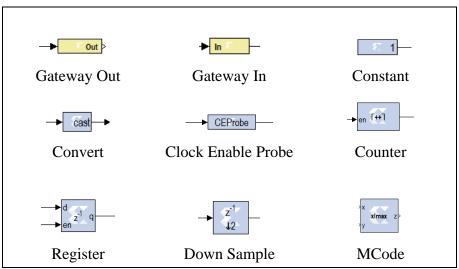

| 4.3. Bloques fundamentales del System Generator | 122 |

| 4.4. Código Frame Generator                     | 127 |

# LISTA DE ILUSTRACIONES

| Figura 1. Sistema de telemetría                                                                | 10     |

|------------------------------------------------------------------------------------------------|--------|

| Figura 2. Sistema de adquisición de a bordo                                                    | 10     |

| Figura 3. Flujo de mediciones en formato TDM                                                   | 11     |

| Figura 4. Diagrama en bloques de un Puesto de Tierra                                           | 12     |

| Figura 5. Circuito puente básico de galgas extensiométricas                                    | 13     |

| Figura 6. Diferentes tipos de modulación                                                       | 14     |

| Figura 7. Ejemplo de señal PDM. Extraído de https://en.wikipedia.org/wiki/P                    | ulse-  |

| density_modulation                                                                             | 14     |

| Figura 8. Códigos de datos PCM                                                                 | 15     |

| Figura 9. Conmutación básica con sincronismo de trama                                          | 16     |

| Figura 10. Esquema general de una super-conmutación                                            | 17     |

| Figura 11. Efectos en una señal PCM. Extraído de (Halsall, 1995) Figura 2.6, Pág. 32           | 19     |

| Figura 12. Rendimiento teórico de probabilidad de error de bits de para diversas técnicas en I | PCM    |

| (suponiendo una perfecta sincronización de bits). Extraído de (Telemetry Standars, 2015)       | 20     |

| Figura 13. Estados en la sincronización de tramas (los números en violeta indican la cantida   | ıd de  |

| tramas válidas que deben estar presentes para poder pasar al próximo estado, los celestes inc  | lican  |

| números de tramas invalidas)                                                                   | 21     |

| Figura 14. Esquema general de un PLD visto como caja negra                                     | 28     |

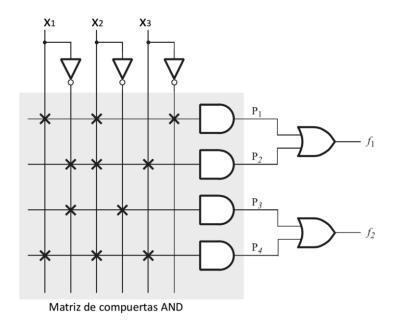

| Figura 15. Estructura general de un PLA                                                        | 29     |

| Figura 16. Diagrama a nivel de compuertas de un PLA                                            | 30     |

| Figura 17. Ejemplo de implementación en una PAL cumpliendo una función determinada             | 31     |

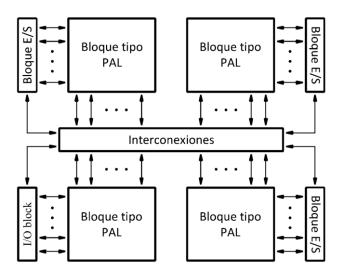

| Figura 18. Estructura genérica de un CPLD                                                      | 32     |

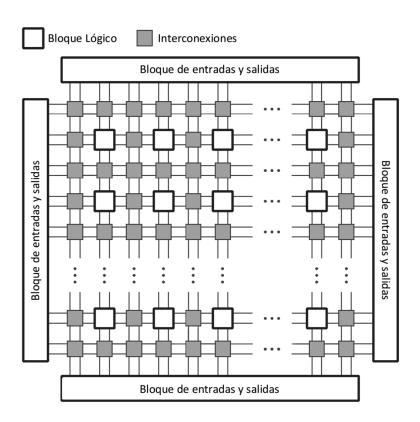

| Figura 19. Estructura general de un FPGA                                                       | 33     |

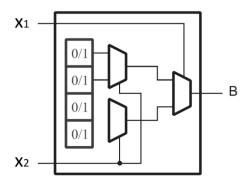

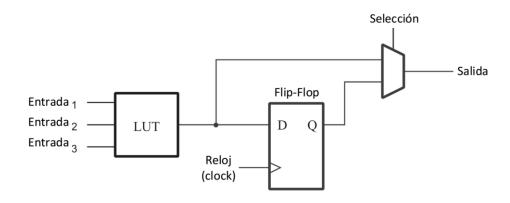

| Figura 20. Circuito para una LUT de dos entradas                                               | 34     |

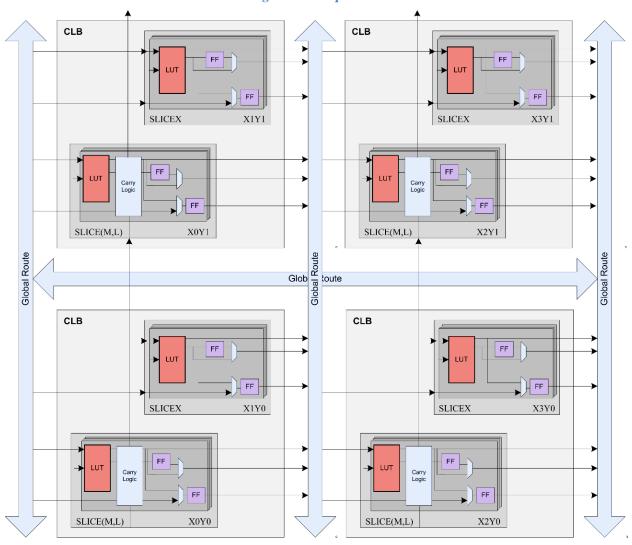

| Figura 21. Bloque CLB                                                                          | 35     |

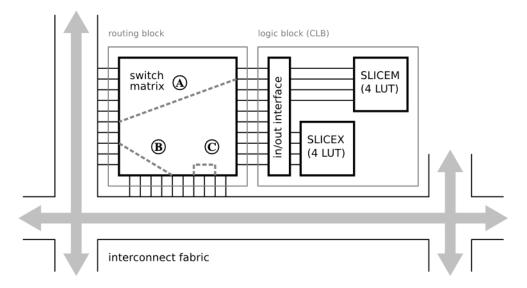

| Figura 22. Organización de LUTs y CLBs en la familia Spartan-6 de Xilinx                       | 35     |

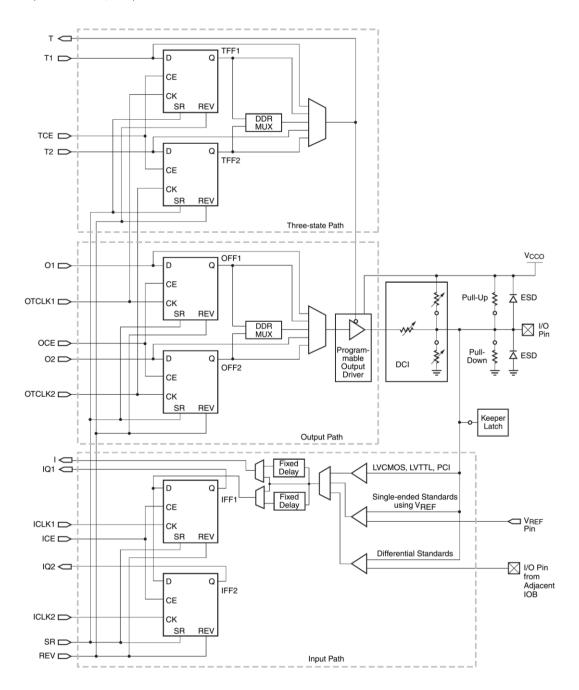

| Figura 23. Esquema simplificado de un IOB de la familia Spartan de Xilinx                      | 36     |

| Figura 24. Enrutamiento en una FPGA Spartan de Xilinx                                          | 37     |

| Figura 25. Niveles de abstracción entre Verilog y VHDL. Extraído de (Maxfield, 2004)           | 41     |

| Figura 26. Flujo de diseño utilizando ISE. Extraído de (Xilinx Inc., s.f.)                     | 42     |

| Figura 27. Vista de un proyecto utilizando la Suite ISE de Xilinx. Extraído de (Xilinx Inc.,   | s.f.). |

|                                                                                                | 43     |

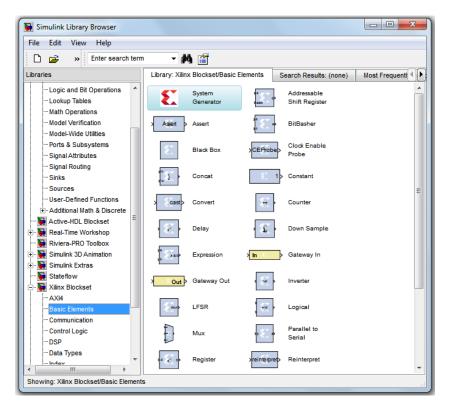

| Figura 28. Flujo de diseño utilizando las herramientas de System Generator                     | 46     |

| Figura 29. Vista de los bloques que componen la libreria System Generator de Xilinx.  | Extraído de   |

|---------------------------------------------------------------------------------------|---------------|

| (Xilinx Inc., s.f.).                                                                  | 47            |

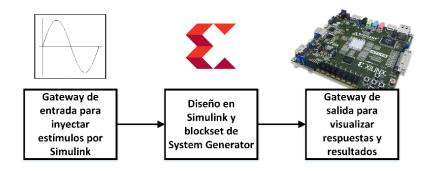

| Figura 30. Concepto de los Gateways de System Generator                               | 47            |

| Figura 31. Placa de desarrollo Atlys con una FPGA Spartan-6 de Xilinx                 | 49            |

| Figura 32. Esquema de puertos disponibles en un kit Atlys                             | 50            |

| Figura 33. Placa de desarrollo 3PX1 de la firma Emtech que utiliza una Spartan 6 de X | Kilinx50      |

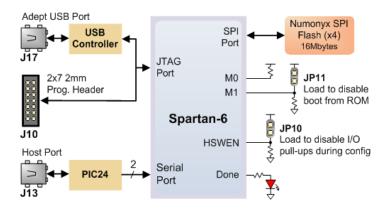

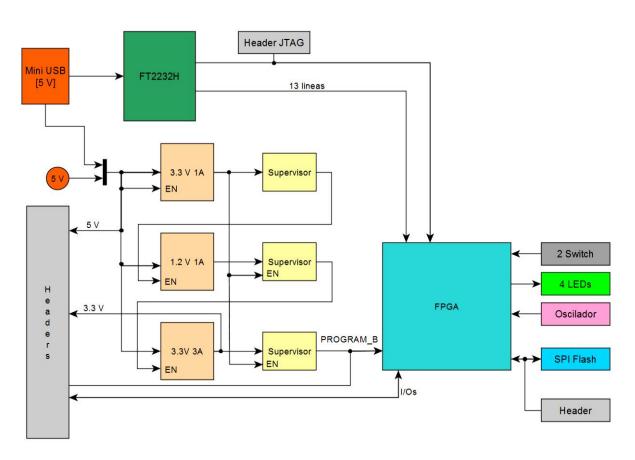

| Figura 34. Arquitectura de la plaqueta 3PX1. Extraído de (Emtech, s.f.)               | 55            |

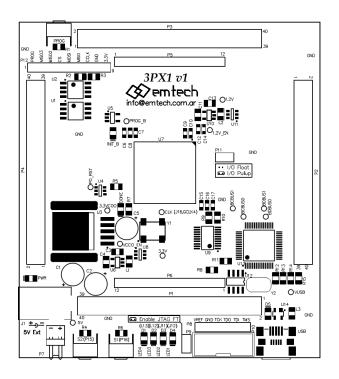

| Figura 35. Diagrama de componentes electrónicos de la plaqueta 3PX1. Extraído de (E   | Emtech, s.f.) |

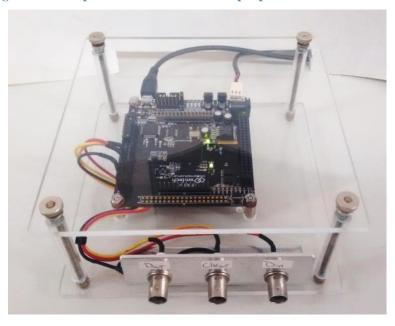

|                                                                                       | 56            |

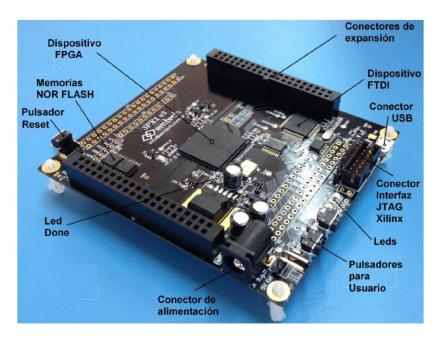

| Figura 36. Vista del kit 3PX1                                                         | 56            |

| Figura 37. Conectores externos para el desarrollo en el kit FPGA                      | 56            |

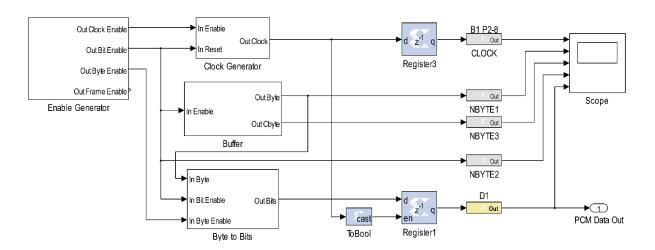

| Figura 38. Diagrama en bloques del simulador                                          | 60            |

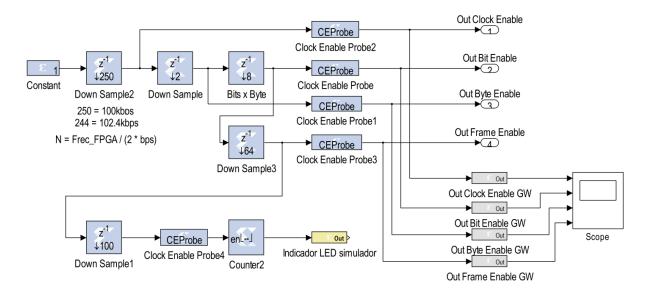

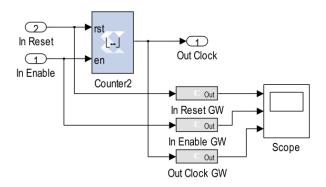

| Figura 39. Desarrollo del sub-sistema Enable Generator                                | 62            |

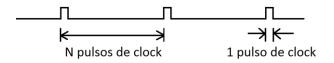

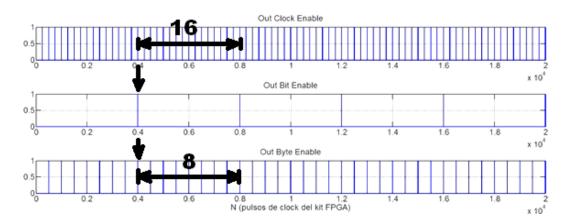

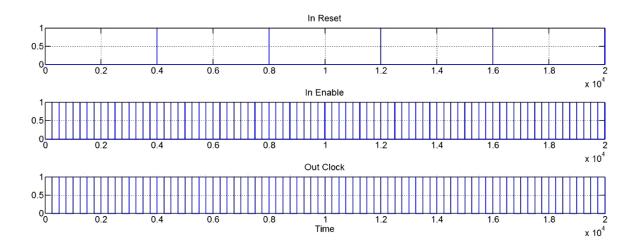

| Figura 40. Salida "Out Clock Enable"                                                  | 62            |

| Figura 41. Salidas del sub-sistema "Enable Generator"                                 | 63            |

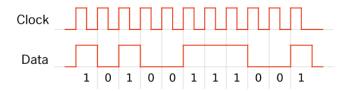

| Figura 42. Datos y "Clock" sincrónicos                                                | 64            |

| Figura 43. Modelo del sub-sistema del "Clock Generator"                               | 64            |

| Figura 44. Entradas y salida del "Clock Generator"                                    | 64            |

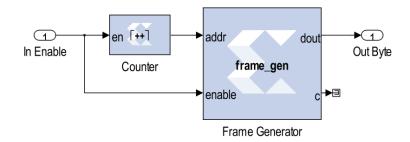

| Figura 45. Modelo del sub-sistema "Buffer"                                            | 65            |

| Figura 46. Modelo del sub-sistema "Byte to Bits"                                      | 66            |

| Figura 47. Señal original transmitida (a) y Señal recibida reducida en ancho de band  | a con ruido   |

| adicional (b)                                                                         | 67            |

| Figura 48. Principio de funcionamiento del sincronizador                              | 67            |

| Figura 49. Señal ruidosa sobre muestreada a 4 y 10 veces la tasa de bit               | 68            |

| Figura 50. Diagrama en bloques del adquisidor                                         | 69            |

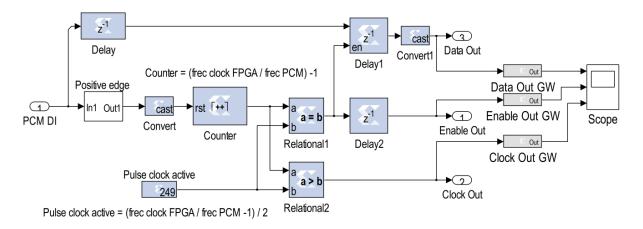

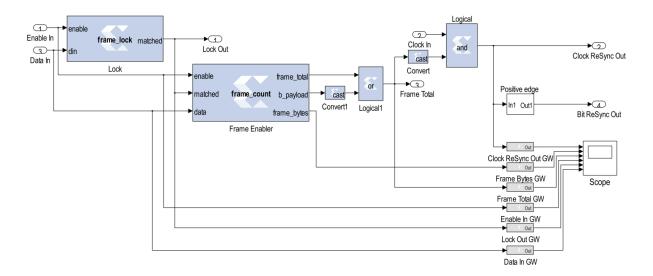

| Figura 51. Modelo del sub-sistema "Clock Sync"                                        | 70            |

| Figura 52. Simulación del sub-sistema "Clock Sync"                                    | 71            |

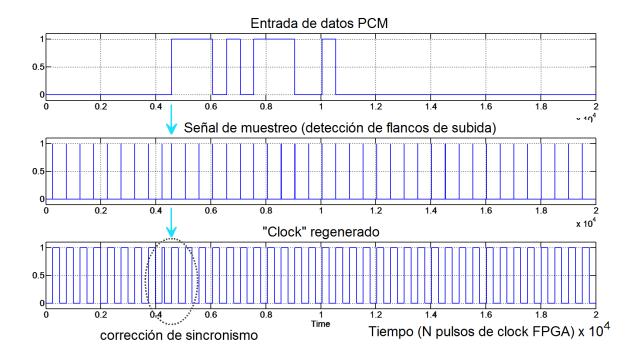

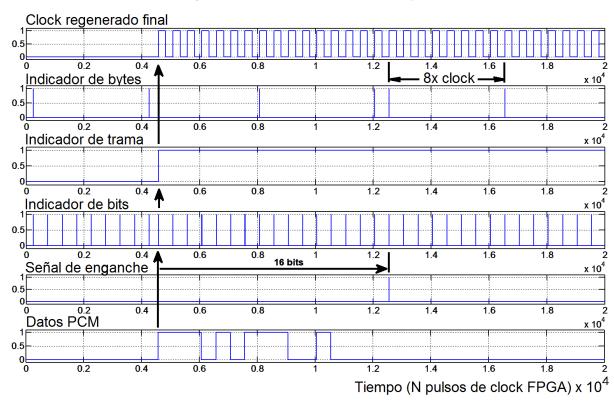

| Figura 53. Modelo del sub-sistema "ReSync"                                            | 72            |

| Figura 54. Resultados del sub-sistema "ReSync"                                        | 72            |

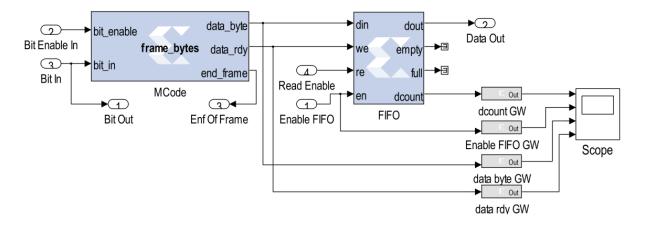

| Figura 55. Modelo del sub-sistema "Store"                                             | 73            |

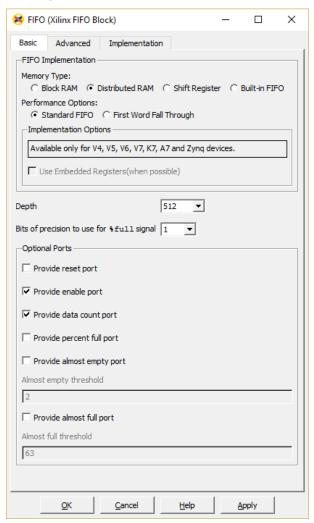

| Figura 56. Cuadro de configuración del bloque FIFO                                    | 74            |

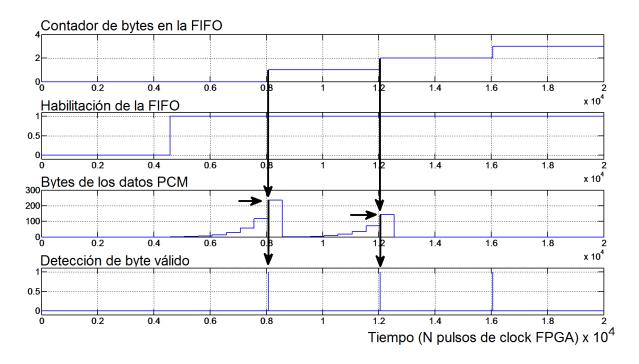

| Figura 57. Resultados de la simulación del sub-sistema "Store"                        | 74            |

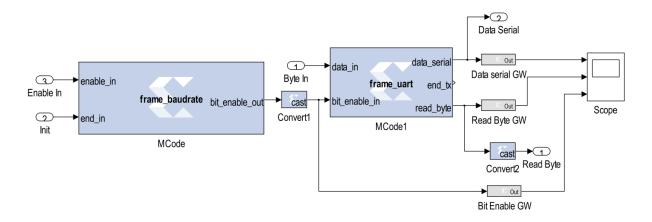

| Figura 58. Modelo del sub-sistema "Send"                                              | 75            |

| Figura 59. Resultados de la simulación del sub-sistema "Send"                         | 75            |

| Figura 60. Medición del tiempo de bit del Transmisor serie a 460800 bps               | 76            |

| Figura 61. Medición del tiempo de bit del Transmisor serie a 230400 bps                    | 77    |

|--------------------------------------------------------------------------------------------|-------|

| Figura 62. Medición del tiempo de bit del Transmisor serie a 115200 bps                    | 77    |

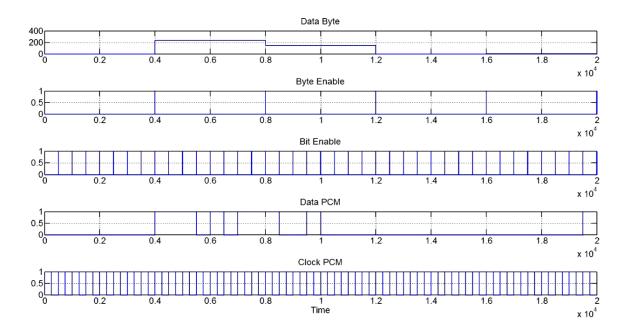

| Figura 63. Señales resultantes de la simulación del sistema simulador PCM                  | 78    |

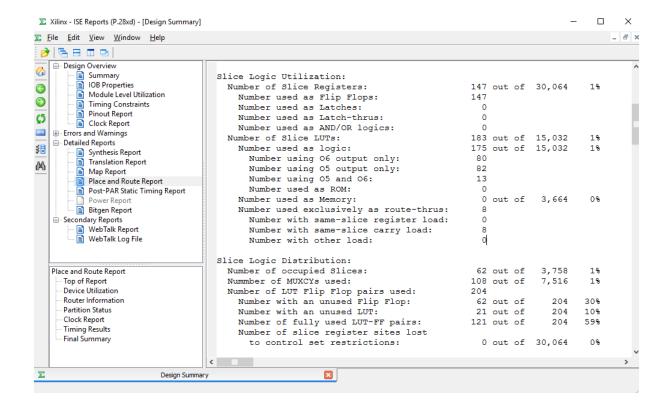

| Figura 64. Resultados del "Place and Route" del simulador PCM                              | 79    |

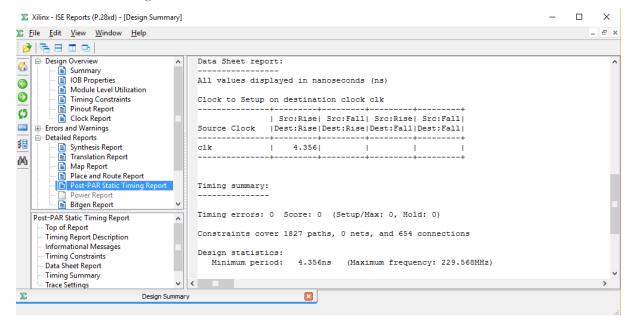

| Figura 65. Resultados de tiempos del "Place and Route" del simulador PCM                   | 79    |

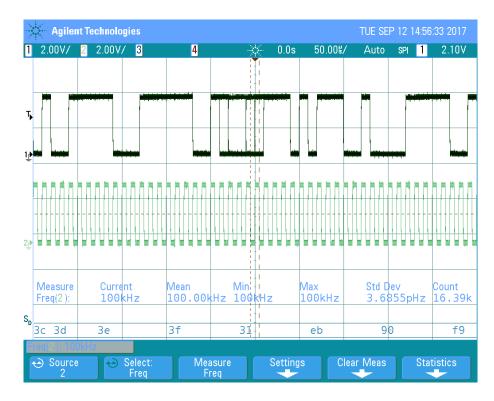

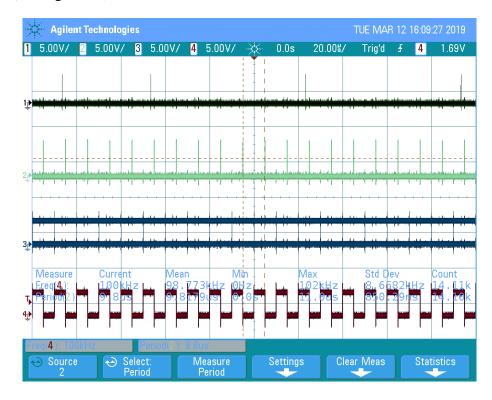

| Figura 66. Medición con osciloscopio del simulador PCM                                     | 80    |

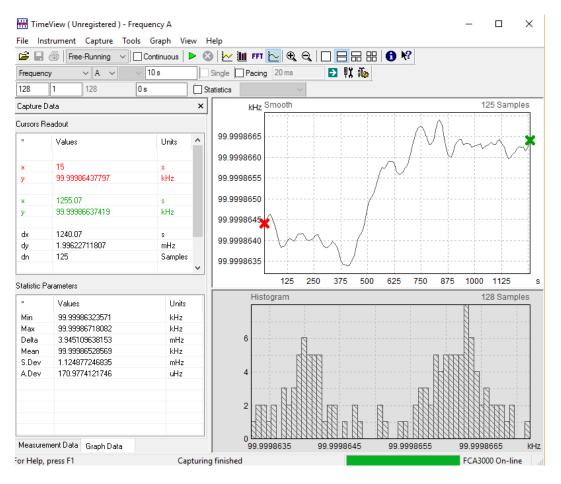

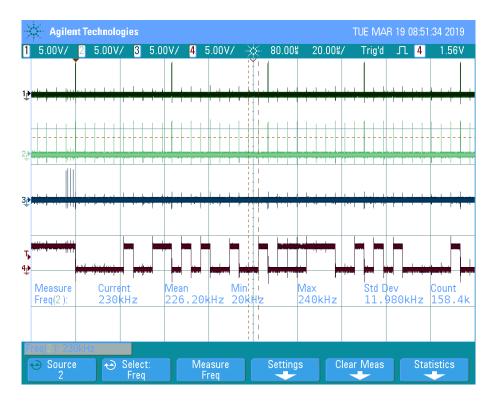

| Figura 67. Medición de la estabilidad del "Clock PCM"                                      | 81    |

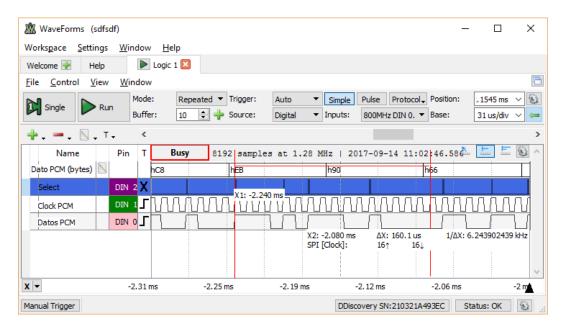

| Figura 68. Medición lógica de los canales de Datos y Clock PCM                             | 82    |

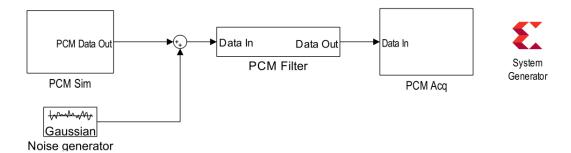

| Figura 69. Implementación del modelo completo                                              | 82    |

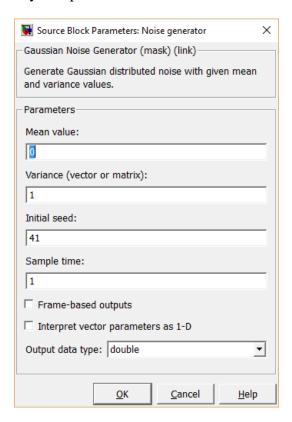

| Figura 70. Valores de "Noise generator"                                                    | 83    |

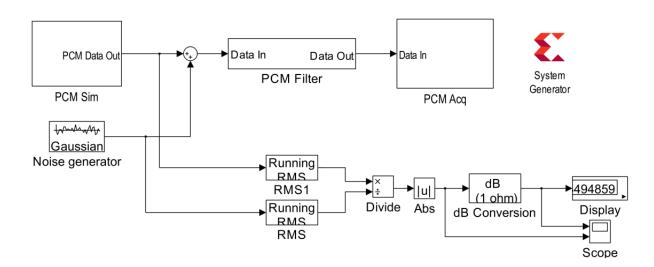

| Figura 71. Modelo para la medición de SNR                                                  | 83    |

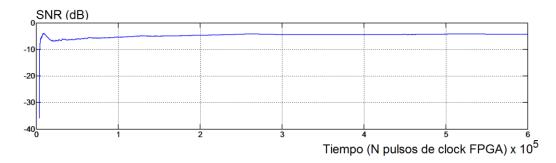

| Figura 72. Medición del SNR a la salida del simulador PCM                                  | 84    |

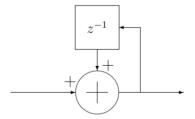

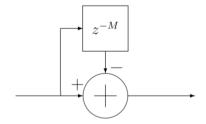

| Figura 73. Diagrama básico de un integrador                                                | 85    |

| Figura 74. Diagrama básico de un comb                                                      | 85    |

| Figura 75. Filtro CIC de 3 etapas                                                          | 86    |

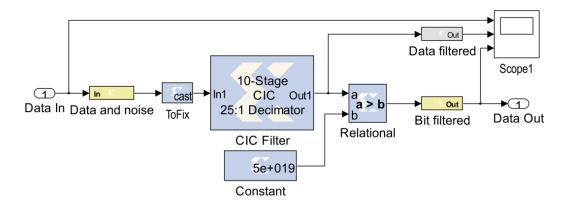

| Figura 76. Modelo del filtro PCM implementado                                              | 88    |

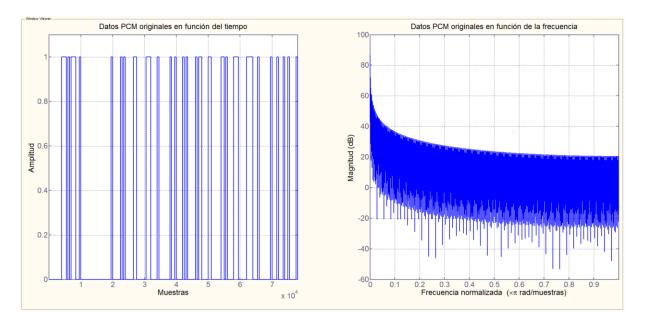

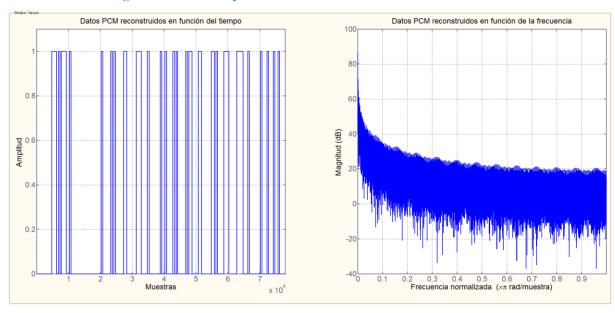

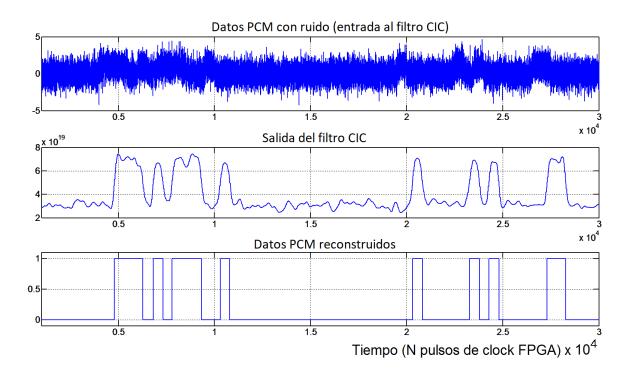

| Figura 77. Análisis espectral de la señal PCM ideal del simulador                          | 89    |

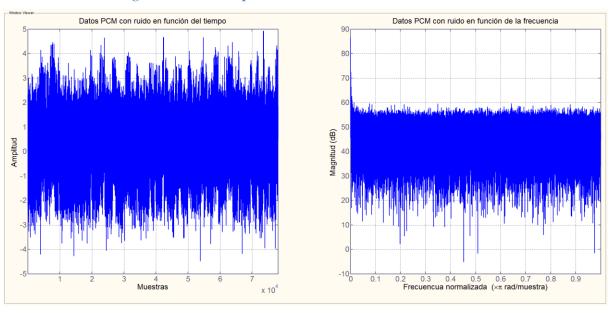

| Figura 78. Análisis espectral de la señal PCM del simulador con ruido gaussiano adicionado | 89    |

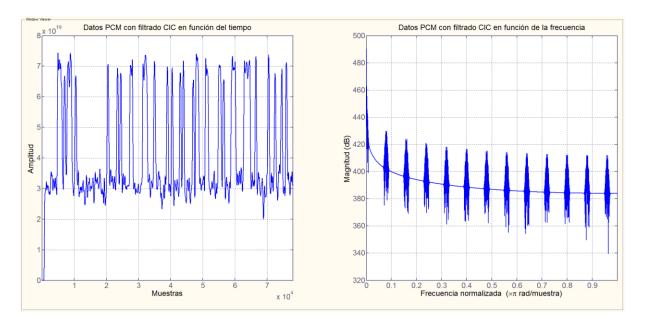

| Figura 79. Análisis espectral de la señal PCM a la salida del filtro CIC                   | 90    |

| Figura 80. Análisis espectral de la señal PCM reconstruida                                 | 90    |

| Figura 81. Medición de la respuesta del filtro PCM en función del tiempo                   | 91    |

| Figura 82. Modelo final de prueba                                                          | 91    |

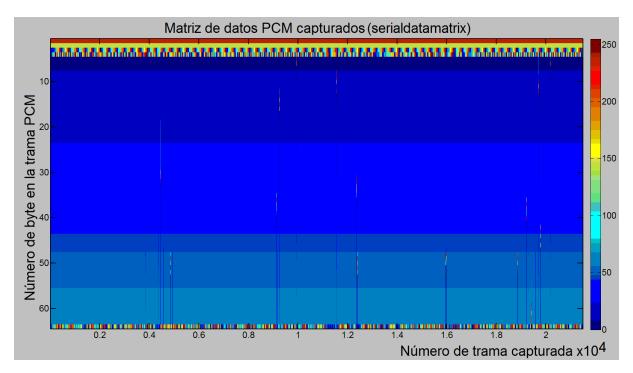

| Figura 83. Imagen de la matriz de datos PCM con escala de colores HSV                      | 92    |

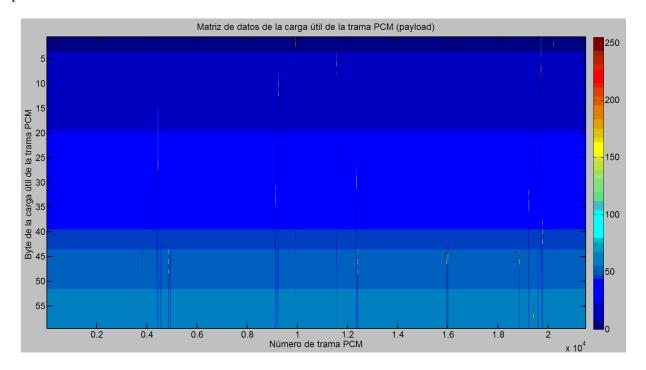

| Figura 84. Imagen de la matriz de la carga útil con escala de colores HSV                  | 93    |

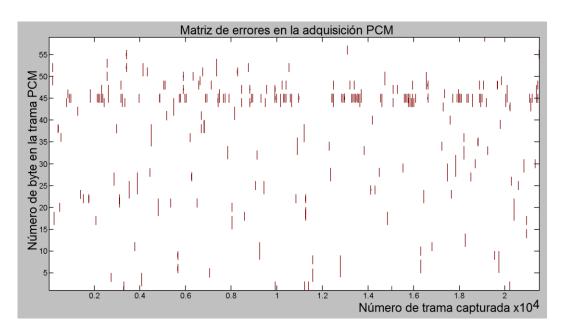

| Figura 85. Mapa de errores encontrados                                                     | 94    |

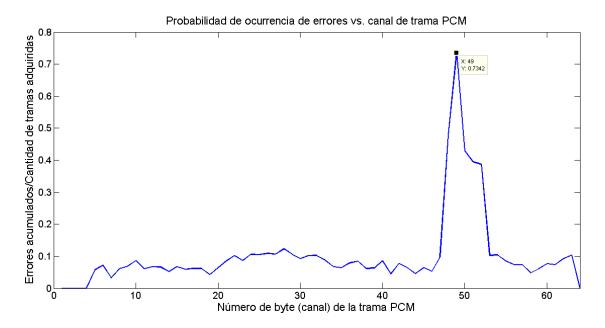

| Figura 86. Probabilidad de ocurrencia de errores en el sistema de adquisición              | 95    |

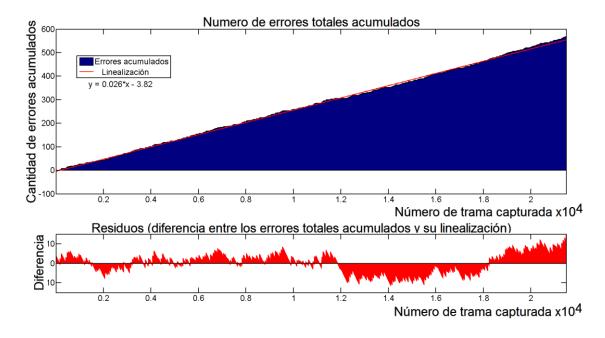

| Figura 87. Errores acumulados totales en la adquisición                                    | 95    |

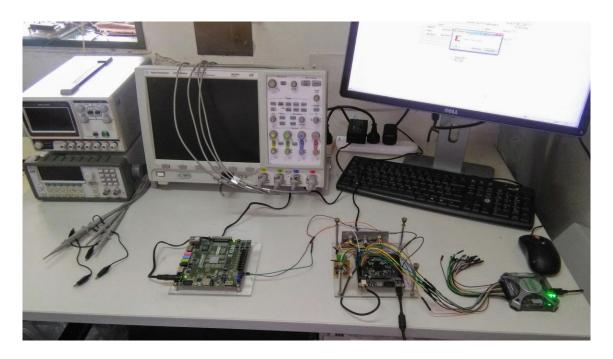

| Figura 88. Banco de pruebas del laboratorio.                                               | 98    |

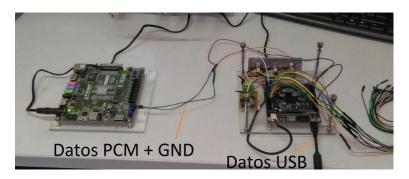

| Figura 89. Generador/Simulador de datos PCM implementado en el kit de desarrollo Atl       | ys de |

| Digilent                                                                                   | 98    |

| Figura 90 Conexión a través de una única línea de datos entre el Simulador implementado o  | on el |

| kit de desarrollo Atlys de Digilent y el adquisidor implementado en el kit 3PX1 de Emtech  | 99    |

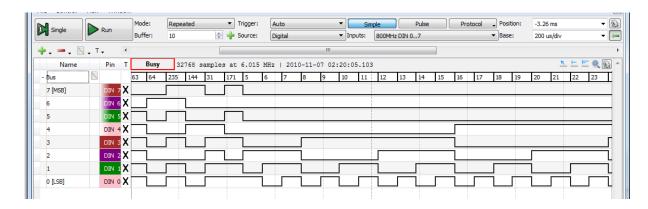

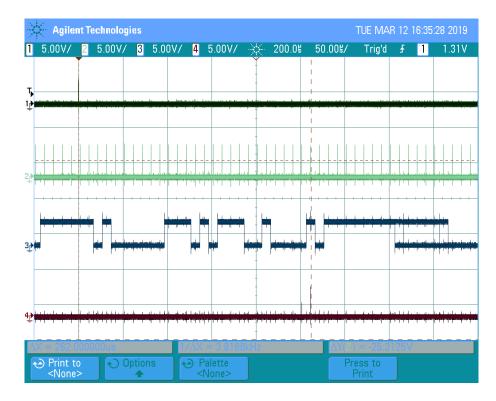

| Figura 91. Análisis del adquisidor con un analizador lógico                                | 100   |

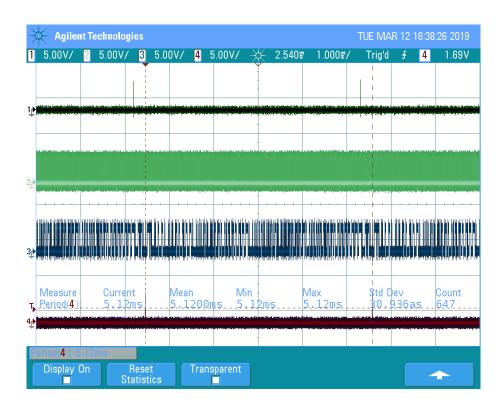

| Figura 92. Medición de la marca de muestreo y el reloj regenerado.                         | 100   |

| Figura 93. Medición del tiempo de detección de la palabra de sincronismo                   | 101   |

| Figura 94. Medición del período entre detecciones de sincronismo                                   | 1  |

|----------------------------------------------------------------------------------------------------|----|

| Figura 95. Medición del clock regenerado                                                           | 2  |

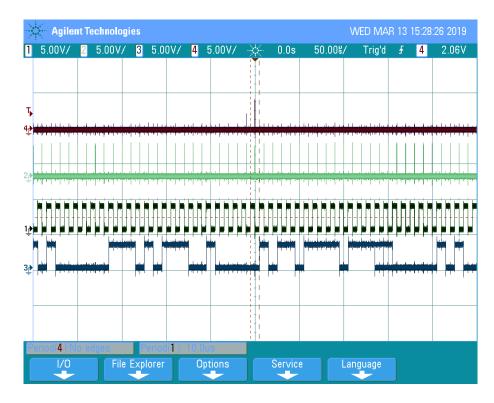

| Figura 96. Medición de la trama UART10                                                             | 2  |

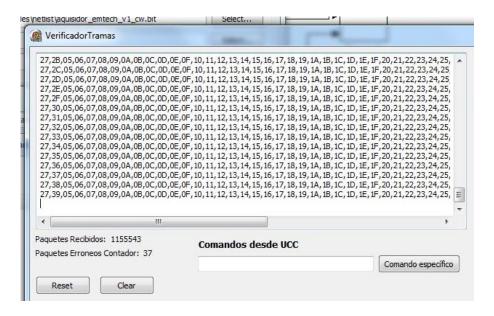

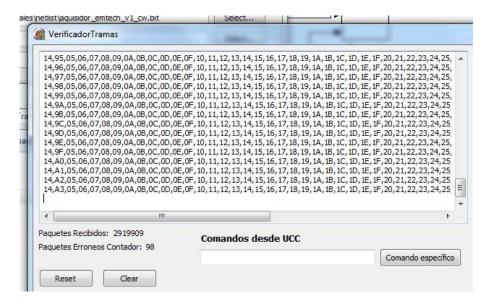

| Figura 97. Verificación de tramas. El simulador se conecta directamente al adquisidor 10           | 3  |

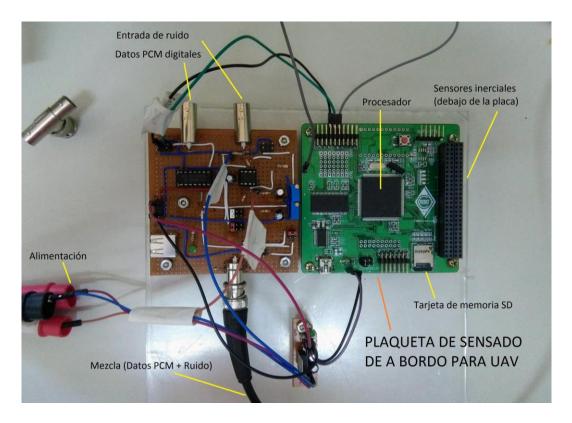

| Figura 98. Plaqueta generadora de datos PCM con sensores integrados para aplicación con UAV        | s  |

| 10                                                                                                 | 4  |

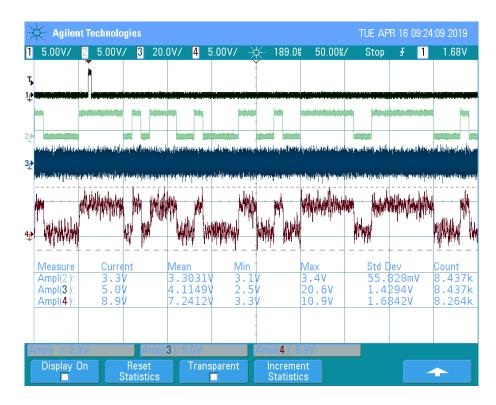

| Figura 99. Adición de ruido en los datos PCM.                                                      | 5  |

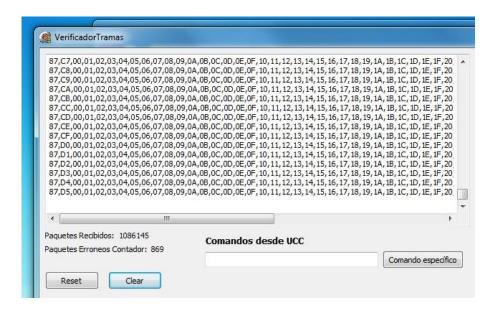

| Figura 100. Verificación de tramas. La plaqueta de abordo con tramas simuladas y sin presenci      | ia |

| de ruido se conecta al adquisidor                                                                  | 6  |

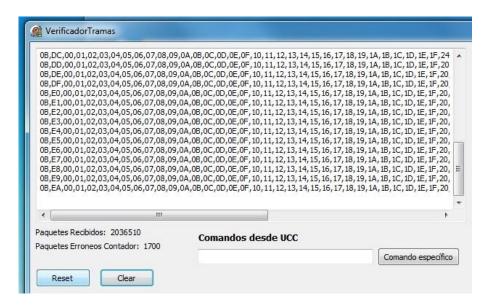

| Figura 101. Verificación de tramas. La plaqueta de abordo con tramas simuladas y con la presenci   | ia |

| de ruido se conecta al adquisidor                                                                  | 6  |

| Figura 102. Verificación de tramas. La plaqueta de abordo con tramas simuladas y datos pseudo      | )- |

| aleatorios y con presencia de ruido se conecta al adquisidor                                       | 7  |

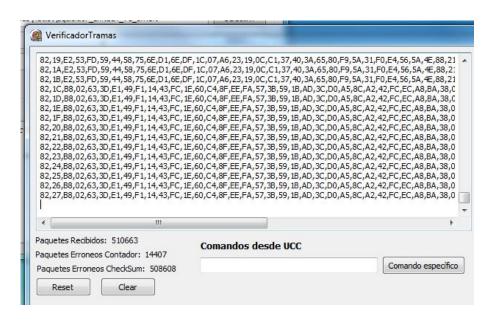

| Figura 103. Verificación de tramas. La plaqueta de abordo con datos reales de sus sensores interno | S  |

| y con presencia de ruido se conecta al adquisidor                                                  | 7  |

| Figura 104. Bloques System Generator de Xilinx para Simulink                                       | 2  |

# LISTA DE TABLAS

| Tabla 1. Patrones de sincronismo recomendados por el estándar IRIG106 | 17  |

|-----------------------------------------------------------------------|-----|

| Tabla 2. Parámetros en función de la velocidad de transmisión         | 75  |

| Tabla 3. Tiempos mínimos y máximos de bit para transmisión serie      | 76  |

| Tabla 4. Versión de software para síntesis y dispositivo FPGA         | 78  |

| Tabla 5. Formato de datos de la Trama PCM                             | 118 |

| Tabla 6. Detalle del canal de IMU                                     | 119 |

| Tabla 7. Pines del modelo asignados a puertos físicos del 3PX1        | 120 |

### INTRODUCCIÓN

### ANTECEDENTES Y FUNDAMENTOS.

Desde el año 2009 en el Departamento de Electrónica Aplicada que pertenece a CITEDEF (Instituto de Investigaciones Científicas y Técnicas para la Defensa), se realizan proyectos de I+D asociados a vectores y vehículos no tripulados (tales como cohetes sonda y sistemas asociados a vectores de aplicaciones civiles y militares), obteniéndose y procesándose las señales y datos de todos los sensores incorporados al vehículo. Además, se adquieren y procesan señales y datos de interés provenientes de otros experimentos científicos que dichos vehículos llevan a bordo. Toda esta información permite obtener, en tiempo real, las coordenadas y trayectoria del vehículo, su "status" interno y todas las variables y parámetros del medio ambiente que rodea al mismo. Antiguamente se trabajaba con el estándar RS232 para la navegación y monitoreo del vehículo, utilizar este tipo de sistemas, en la actualidad, implicaría una limitación importante en la transferencia de datos. Hoy en día esta limitación se supera trabajando sobre una red Ethernet, es por ello que muchas estaciones de monitoreo en tierra, cuentan con esta arquitectura de red a fin de adquirir dichas tramas digitales y realizar un procesamiento en tiempo real.

En el año 2014, surge la necesidad por parte de CITEDEF de realizar un sistema de adquisición de datos serie para la medición remota de magnitudes físicas en sistemas de sondeo no tripulados (cohetes sonda) y en vehículos en general, de tal manera que el sistema permita procesar señales de alta velocidad, con una baja tasa de pérdidas de datos; y así poder manejar tramas digitales de mayor tamaño y redistribuirlas por una red Ethernet.

La aplicación de estos sistemas de adquisición en la transmisión y recepción de datos, ha permitido, no solamente el incremento de la tasa efectiva de datos y el ancho de banda en la trasmisión de información desde el vehículo y hacia el puesto de monitoreo remoto (en forma bidireccional), sino también en la implementación de nuevos algoritmos de procesamiento de señales e imágenes que logran una navegación y control más precisos, lo que los posiciona en un lugar de privilegio en los tópicos más avanzados de la ingeniería aeroespacial actual y toma una mayor dimensión al querer adquirir tramas de mayor tamaño en vehículos más complejos y que contengan mayor cantidad de experimentos científicos a bordo.

Este tipo de Sistema Telemétrico de Adquisición de Datos con un muy alto grado de procesamiento de señales en tiempo real no está desarrollado en el país. Son muy escasos los grupos de Investigación y Desarrollo que participan en el desarrollo este tipo de Sistema y por lo general utilizan material importado y sensible para su exportación. El aporte conceptual de esta Tesis será aplicable a diferentes áreas del conocimiento que requieren la integración de este tipo de sistemas

tales como Sistemas de seguimiento de UAVs (Unmanned Aerial Vehicle, Vehículo aéreo no tripulado), Sistemas de monitoreo de cohetes sondas, entre otros. Se debe destacar la importancia en el desarrollo de una estructura de hardware y software como la propuesta para lograr una integración completa en todas las etapas de un vuelo o lanzamiento. Cabe aclarar que el tipo de Sistema de Adquisición propuesto posee características que no se han encontraron en los manuales de los productos internacionales de marcas de primer nivel.

### JUSTIFICACIÓN DEL PROBLEMA

La meta principal del trabajo propuesto se basa en: Realizar un estudio de algoritmos ad-hoc, un desarrollo conceptual y diseño del hardware asociado, la obtención del código para su implementación y la simulación computacional. Para finalmente poder implementar en campo un sistema de adquisición de datos sincrónicos de alta velocidad para medición remota de magnitudes físicas aplicado a unidades y plataformas con movimientos en el espacio.

En la actualidad existen sistemas desarrollados que no son autónomos poseen un complejo algoritmo para la adquisición de datos inaccesible al usuario, el sistema propuesto se destaca ya puede conectarse en cualquier computadora a través de un simple puerto USB y además el usuario puedo modificar el modelo de adquisición adaptándose a sus propios requerimientos. Los fabricantes de este tipo de unidades no permiten definir ni se puede tener acceso a ajustes y/o posibles modificaciones de sus características constitutivas. Es decir que no se pueden definir sus parámetros ni modificar o ajustar sus variables. Estos sistemas se encuentran empaquetados (llave en mano) y solo se accede, en algunos casos, a través de costosas licencias y otras veces solo el fabricante realiza dichas mejoras. Esto representa un grave problema para la construcción de un equipo con un sistema de adquisición y monitoreo de datos llave en mano, por ello, el sistema de adquisición debe ser ad-hoc ya que el mismo necesita tener varios grados de libertad y parametrizaciones específicas en lo que se refiere al estudio del comportamiento de dichos vehículos y al estudio de las magnitudes físicas de los experimentos que se abordan. Utilizar estos sistemas ya existentes implica una seria limitación en los estudios mencionados y un riesgo costoso para los experimentos pertenecientes a la carga útil. Se necesita un Sistema que provea datos sumamente confiables en cuanto a su integridad y calidad.

En los últimos años, se han realizado grandes esfuerzos en el desarrollo de métodos computacionales para resolver las ecuaciones que determinen la posición de un objeto en el espacio (Comas, Vescovo, & Legnani, Análisis del comportamiento caótico del flujo hipersónico en el vector GRADICOM II). Por ello, es sumamente necesario poseer un sistema de desarrollo abierto para poder realizar implementaciones de diversos algoritmos ad-hoc. Por lo tanto, se procederá al

diseño conceptual, construcción de un sistema de desarrollo y programación de nuevos algoritmos

de adquisición de datos con el fin de obtener un sistema autónomo de adquisición de datos

sincrónicos de alta velocidad controlada por FPGA, para implementarlo en la medición remota de

magnitudes físicas y parámetros propios de un vehículo que permita un amplio rango de control

de todas sus mediciones, variables y parámetros en estudio.

Se debe destacar que el Sistema completo será puesto a prueba primero con simulaciones

computacionales y luego con pruebas y ensayos en el Laboratorio antes de utilizarlo en el campo

también. Esto resulta ser una tarea compleja ya que existen diferentes niveles de problemas a

resolver durante los procesos de diseño, sincronización, construcción, programación y ensamble

del sistema global, ya que el mismo consta de varios subsistemas interconectados que deben

funcionar en forma sincrónica, como una única unidad solidaria, y, además, algunos sub-conjuntos

del sistema deberán operar de manera autónoma.

Es sumamente importante destacar que se han escrito tres publicaciones en revistas

internacionales, una particularmente que se trata del tema de tesis en cuestión, y dos que se

desprenden de temas relacionados con la aplicación de esta tesis. El primer artículo se denomina

"Filtering and Acquisition of PCM Frames Using System Generator" y se publicó en la revista

"International Journal of Electronics and Communication Engineering (IJECE)" con ISSN(P):

2278-9901; ISSN(E): 2278-991X en el Vol. 8, Issue 1, Dec - Jan 2019; 1-10 en la ciudad de Tamil

Nadu, India.

International Journal of Electronics and Communication Engineering (IJECE) ISSN(P): 2278-9901; ISSN(E): 2278-991X Vol. 8, Issue 1, Dec - Jan 2019; 1-10

O IASET

International Academy of Science,

Engineering and Technology

Connecting Researchers; Nurturing Innovations

FILTERING AND ACQUISITION OF PCM FRAMES USING SYSTEM GENERATOR

Adrian Stacul & Edgardo Comas

Instituto De Investigaciones Científicas Y Tecnicas Para La Defensa Buenos Aires, Argentina

ABSTRACT

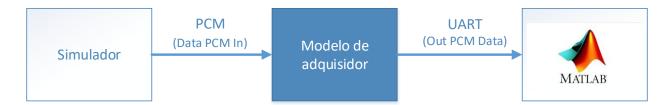

a System Generator and Simulink model. The entire system will be applied to a ground station with an ad-hoc telemetric data acquisition system to be applied in unmanned aerial vehicles, atmospheric sounding rockets and nano-satellites monitoring.

The main purpose of this paper is the design, development, and implementation of a PCM bit-synchronizer based on

Based on this information, the ground station will be able to compute navigation parameters trajectories, velocities and

attitudes. In particular, this PCM module was built to be used in atmospheric sounding vector evaluations by the Instituto de Investigaciones Científicas y Técnicas para la Defensa of Argentina.

KEYWORDS: Bit-Synchronizer, FPGA, Ground Station, PCM Frame, System Generator

3

A su vez, se han escrito dos artículos de proyectos relacionados a esta tesis y aplicación directa de la misma, los mismos ya fueron aceptados, pero aún no están publicados ya que el volumen de la revista no salió al día de la fecha.

El primero de estos de titula "A Hardware System with ARM-based data processing for Nano-Satellites", fue aceptado en Enero del 2020 y se publicará en Julio del 2020 en la revista "International Journal of Reconfigurable and Embedded Systems (IJRES)" con ISSN 2089-4864 en la ciudad de Yogyakarta, Indonesia.

### A Hardware System with ARM-based data processing for Nano-Satellites

Adrián Stacul \*, Daniel Pastafiglia\*, Ariel Dalmas Di Giovanni\*, Martín Morales\*, Sergio Saluzzi\*, Gerardo García\*, Agustín Gadea\*\* and Ramiro Puga\*\*

\* Digital Techniques Laboratory, Institute of Scientific and Technical Research for Defense (CITEDEF)

| cientific and Technical Research for Defense in Argentina igaciones Cientificas y Técnicas para la Defensa - CITEDEF) is essing hardware module based on a ARM Cortex the TMicroelectronics. The microcontroller (MCU) has the amaximum clock frequency of 180 MHz, integrates at (FPU). An 8MB SDRAM was included for dynamic data                                              |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| tessing hardware module based on a ARM Cortex M4<br>TMicroelectronics. The microcontroller (MCU) has the<br>tamaximum clock frequency of 180 MHz, integrates a                                                                                                                                                                                                                   |  |  |  |

| a maximum clock frequency of 180 MHz, integrates a                                                                                                                                                                                                                                                                                                                               |  |  |  |

| (FPU). An 8MB SDRAM was included for dynamic data                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Floating Point Unit (FPU). An 8MB SDRAM was included for dynamic data allocation. This hardware will host and process the algorithms to calculate and determine the nanosatellite's attitude. The module is intended to be Cubesat compatible, possess a flexible design, handles various inertial sensors and can manage backups on microSD memory cards with sizes up to 32GB. |  |  |  |

| Time toob memory cards with sizes up to 52ds.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| right © 201x Institute of Advanced Engineering and Science.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| All rights reserved.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

El segundo artículo tiene como título "Robust Object Tracking in Infrared Video via Particle Filters" aceptado en la revista "Electronic Letters on Computer Vision and Image Analysis" (ELCVIA) con ISSN 1577-5097 en la ciudad de Barcelona, España.

<sup>\*\*</sup> Electronics department, National Technological University (UTN)

### Robust Object Tracking in Infrared Video via Particle Filters

Edgardo Comas\*, Adrián Stácul\* and Claudio Delrieux+

- \* Instituto de Investigaciones Científicas y Técnicas para la Defensa, San Juan Bautista de La Salle 4397 Villa Martelli, Buenos Aires, Argentina.

- \* Universidad Tecnológica Nacional, Facultad Regional Buenos Aires, Medrano 951, Buenos Aires, Argentina.

- + Universidad Nacional de Sur, Laboratorio de Ciencias de las Imágenes, and CONICET, Avenida Colón 80 -Bahía Blanca, Argentina.

Received 1 September 2019; revised 1; accepted 1

#### Abstract

In this paper we investigate the effectiveness of particle filters for object tracking in infrared videos. Once the user identifies the target object to be followed in position and size, its most representative feature points are obtained by means of the SURF algorithm. A particle filter is initialized with these feature points, and the location of the object within the video frames is determined by the average value of the particles that have a greater similarity with the target. Our aim is to make possible unnupervised object tracking in unmanned night flights. Two different field tests were carried out to study the filter behaviour in comparison with previously used methods in the bibliography. The first one was tracking an unmanned aerial vehicle (UAV) in the open. The second one was to identify a heliport in a noisy infrared zenithal video take. In the first test, the UAV was followed by another positioning system simultaneously, thus allowing the comparison of both systems, and the evaluation in the improvement introduced by the particle algorithm.

Key Words: Image Analysis, Pattern Recognition, Tracking, Particle Filter

#### ESTADO DEL ARTE

En la actualidad, el procesamiento digital de señales se realiza por medio de dispositivos electrónicos como las FPGA, entre otros, que ya estas vienen implementadas en plaquetas o kits de desarrollo (Rojas, Franco M, & Pateti M, 2009). Un ejemplo es el caso específico de la familia "Spartan" de la firma Xilinx, estas FPGA son ampliamente utilizadas en aplicaciones de dispositivos como sistemas embebidos, control, sistemas de adquisición de datos y telecomunicaciones. Este tipo de plaquetas nos otorga versatilidad y escalabilidad al momento del diseño y desarrollo de la solución a implementar, y también nos otorga portabilidad y escalabilidad a futuro ya que no queda atado a un dispositivo puntual, sino que es transferible a otros nuevos dispositivos FPGA.

El FPGA es un dispositivo de fácil programación y mediante Lenguajes de Descripción de Hardware (HDL) y Co-Simulación utilización MATLAB. Su principal ventaja es que puede programarse múltiples veces bajando los costos cuando en el diseño se encuentran fallas y el sistema requiera ser actualizado y reprogramado.

Generalmente, en los sistemas diseñados para el procesamiento digital de señales se debe realizar un estudios minucioso y exhaustivo a priori para elegir un dispositivo que satisfaga las necesidades

del proyecto. Este puede tener características tales como: conversores, filtros digitales y sistemas de procesamiento integrados, para que en el tratamiento de la señal se pueda llegar a un trabajo menos extenso y más confiable debido a sus altas tasas de muestreo, velocidad de procesamiento, y grandes cantidades de bits a manejar que implican una menor pérdida de información y de calidad a comparación con sistemas microcontrolados antiguos.

Este proyecto no solamente pretende realizar un prototipo experimental de adquisición de datos, sino de dotar al Laboratorio de Técnicas Digitales de CITEDEF de una técnica nueva como es la de la implementación de código FPGA mediante la herramienta System Generator (Xilinx Inc., s.f.) para acelerar tareas de desarrollo. A su vez, este trabajo involucra la realización de pruebas de campo con vehículos no tripulados reales.

#### **OBJETIVOS**

El sistema de adquisición de datos sincrónicos de alta velocidad, que se propone desarrollar posee: algoritmos complejos que manejan el control del sistema, la adquisición de datos y la distribución de información desde y hacia las múltiples plataformas de operación. En la actualidad los sistemas comerciales equivalentes no tienen disponibles dichos algoritmos para ser modificados y/o reprogramados por el usuario, son considerados por los países desarrollados como unidades tecnológicas sensibles a la exportación, por lo tanto, son productos llave en mano. Los ajustes, modificaciones y/o adaptaciones solamente pueden ser realizados por el fabricante para lo cual hay que pagar costosas licencias que, por lo general, se renuevan anualmente.

Los sistemas comerciales equivalentes resultan ser muy costosos solo permiten que el usuario acceda a partes accesorias del software, pero no cumplen para nada con los requerimientos planteados en los objetivos. Esto genera un grave problema cuando se quiere implementar un sistema de adquisición y monitoreo de datos de alta velocidad, ya que el mismo necesita tener muchos grados de libertad en lo que se refiere al estudio del comportamiento de vehículos autodirigidos (como el UAV) y al estudio de las magnitudes físicas de los experimentos que se van a lleva abordo. Por ello, el objetivo primario de este trabajo de tesis representa al mismo tiempo un desafío tecnológico y un desarrollo de punta ya que el sistema a construir, deberá manejar palabras de datos entre 8 y 32 bits con velocidades de transferencia en el orden de los Mbits/s y que esta transferencia de información desde y hacia el vehículo autónomo, se realice en tiempo real, lo cual sería imposible implementar con un sistema comercial por los motivos ya descritas anteriormente. Para ello se va a trabajar con sistemas embebidos (en particular una FPGA de la empresa Xilinx).

Los objetivos específicos son:

- ✓ Desarrollar un método sistemático para recepción y sincronización de tramas telemétricas PCM de código NRZ-L sin pérdida de datos.

- ✓ Desarrollar un serializador de datos que permita la traducción de tramas PCM sincronizadas a una interface de datos USB serie mediante el estándar RS-232 y un puerto virtual.

- ✓ Determinar las métricas necesarias y ensayos específicos para validar la síntesis circuital, en una FPGA, obtenida a partir del método desarrollado.

- ✓ Implementar el desarrollo necesario en un kit de evaluación con una FPGA de bajo costo y contextualizarlo en un escenario real de trabajo para pruebas de campo.

#### Los alcances son:

✓ Consolidar la capacidad científica/técnica en materia de la sincronización a nivel de bit de tramas PCM mediante herramientas de diseño, simulación y ensayos con tecnología FPGA, a los efectos de poder determinar remotamente las magnitudes físicas de vectores y vehículos aéreos en general, específicamente trayectorias, velocidades y actitudes de los mismos, con base en la solución matemática de ecuaciones relacionadas, el procesamiento de señales de sensores específicos y la implantación de un puesto de monitoreo y supervisión desde tierra.

## **METODOLOGÍA**

Con el fin de crear unas bases de conocimiento y avance en FPGA, se requiere implementar un sistema de adquisición (mencionado anteriormente) que procese las tramas telemétricas y cumpliendo las necesidades básicas que esto implica, como la calidad y la integridad de datos hacia el usuario. El presente proyecto se dividió en etapas que permitieran facilitar su ejecución, algunas de ellas son:

- 1. Investigación sobre la temática de telemetría, enfocándose a las estaciones de tierra y la adquisición de datos.

- 2. Investigación sobre el desarrollo de modelos en FPGA como nueva tecnología aplicada a la adquisición de señales de telemetría PCM.

- 3. Sistemas simuladores de datos PCM y procesamientos previos y conversiones asociadas.

- 4. Bloques de programación de FPGA incorporando la técnica de Matlab/Simulink.

- 5. Verificación y pruebas de campo.

## CAPITULO 1 - SISTEMAS DE TELEMETRÍA

La telemetría es el proceso por el cual se miden ciertas características de un objeto (por ejemplo, la velocidad de un avión), y los resultados son transmitidos a una estación remota en tierra donde se visualizan, registran y analizan los mismos. Los medios de transmisión pueden ser alámbricos para entornos terrestres estáticos (e.g. plantas generadoras de energía), aire o el espacio para aplicaciones de vehículos aéreos o satélites.

Para poder entender el objeto de estudio de esta tesis se debe comprender, con anticipación, como opera un sistema de telemetría en su totalidad ya que el desarrollo planteado se lo someterá a pruebas de campo.

En la actualidad, en las aplicaciones de telemetría que soportan un gran número de mediciones, sería muy costoso e impracticable utilizar un canal de trasmisión diferente para cada una de las mediciones. El proceso de telemetría involucra agrupar las mediciones (como ser, presiones, velocidades y temperaturas) en un formato determinado para poder ser trasmitidas en una única trama o flujo de datos. Una vez recibido, la trama de datos se descompone recuperando cada una de las mediciones originales para su análisis posterior.

La telemetría permite estar en un lugar seguro (o conveniente) durante el seguimiento de lo que está ocurriendo en un lugar inseguro (o inconveniente). El desarrollo de vehículos aéreos, por ejemplo, es una de las principales aplicaciones de los sistemas de telemetría. Durante cierta prueba, una aeronave realiza una variedad de maniobras de vuelo. Los datos críticos de tales maniobras de vuelo se transmiten a una estación en tierra donde los ingenieros y técnicos de pruebas de vuelo visualizan los resultados en tiempo real y pueden ser analizados. El monitoreo en tiempo real permite tomar decisiones instantáneas sobre si se procede o se abandona la misión. Con el análisis en tiempo real, el ingeniero de pruebas de vuelo podrá solicitar que se repita una maniobra determinada, analizarla, aprobar los resultados o sustituirla con un plan de prueba alternativo. Los datos en tiempo real también se pueden capturar y guardar en medios de almacenamiento para un análisis posterior.

## 1.1. DESCRIPCIÓN GENERAL DE UN SISTEMA DE TELEMETRÍA

Hoy en día, los sistemas de telemetría son productos del tipo COTS (Commercial Off-The-Shelf), es decir, productos comerciales diseñados para ser implementados fácilmente en sistemas existentes sin la necesidad de un producto personalizado para tal fin (McKinney, 2001). Sin embargo, a pesar de que todos estos productos tengan muchos elementos en común, en el campo

científico se requiere de un desarrollo específico de telemetría únicamente para cumplir los requisitos de la aplicación a la cual se dará uso.

Un sistema de telemetría muchas veces es vista como dos grandes componentes, el sistema de a bordo y la estación o puesto de tierra (Figura 1). En la actualidad, cualquiera o ambas pueden estar en el aire o en el terreno (Comas, Pastafiglia, Bruña, Dalmas Di Giovanni, & Stacul, 2015).

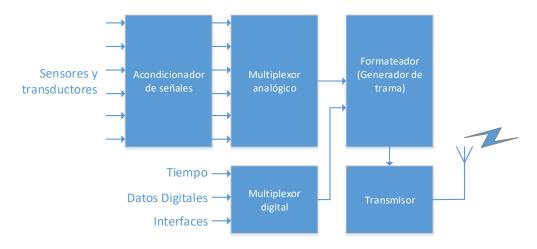

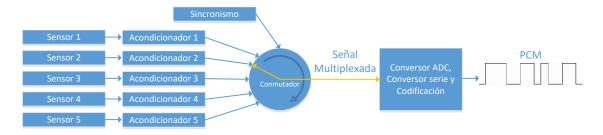

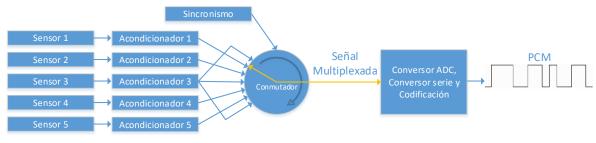

Figura 1. Sistema de telemetría

El sistema de adquisición de a bordo (Figura 2) comienza cuando los sensores (transductores) miden la magnitud o atributo físico y lo transforman en un valor eléctrico. Algunos sensores producen una tensión eléctrica directamente (sensores de termocuplas para medir temperatura o medidores de deformación piezoeléctrica para medir aceleraciones), mientras que otros necesitan de alguna excitación (medidores de tensión resistivos, potenciómetros de rotación, etc.). Los sensores generalmente están conectados a acondicionadores de señales, los cuales proveen energía a estos para operar y ser compatibles con la próxima etapa de adquisición.

El multiplexor toma cada una de las mediciones analógicas y produce un único flujo de pulsos con una tensión eléctrica relativa a la medición del canal. Esta rigurosa fusión de datos en una única serie de pulsos se denomina "Multiplexación por División de Tiempo" ó TDM (Time Division Multiplexing).

Figura 2. Sistema de adquisición de a bordo

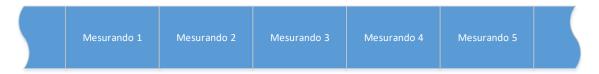

La configuración en la que la altura del pulso del flujo TDM es proporcional al valor de la medición se denomina "Modulación por Amplitud del Pulso" (PAM – Pulse Amplitude Modulation). A dicha señal se concede un único set de pulsos con el fin de identificar la fuente de medición respecto del valor de dicha medición (Schwartz). La modulación PAM posee muchas limitaciones, la cual incluye la precisión, el número de mediciones que soporta y una pobre capacidad de integrarse a señales digitales. Hoy en día se utiliza la "Modulación por Pulsos Codificados" (PCM - Pulse Code Modulation) para sistemas de telemetría (Consultative Committee for Space Data Systems, 2000), donde se tiene una alta precisión, donde existe una resolución limitada por el conversor analógico-digital ADC (Analog to Digital Converter), y cientos de mediciones pueden ser adquiridas a lo largo de la trama digital desde múltiples fuentes, incluyendo datos y memoria de la computadora de a bordo (Figura 3).

Figura 3. Flujo de mediciones en formato TDM

En un sistema basado en PCM, la salida PAM original del multiplexor es digitalizada a formato paralelo. Esto, junto a otras fuentes de datos digitales, se fusionan y formatean con algún dato de sincronismo para la identificación del mesurando. La salida del formateador serializa el flujo de datos paralelos en una cadena de datos binarios para su transmisión en el medio elegido. Todos los componentes a partir de los sensores hasta el formateador comprenden el "Encoder" (Codificador). Existen otros "Encoders" remotos que a menudo se utilizan para multiplexar datos de sensores adicionales en la salida del codificador principal, esto no solamente se utiliza para ampliar el número de mediciones, sino que también para eliminar el recorrido de cables requeridos para cada sensor.

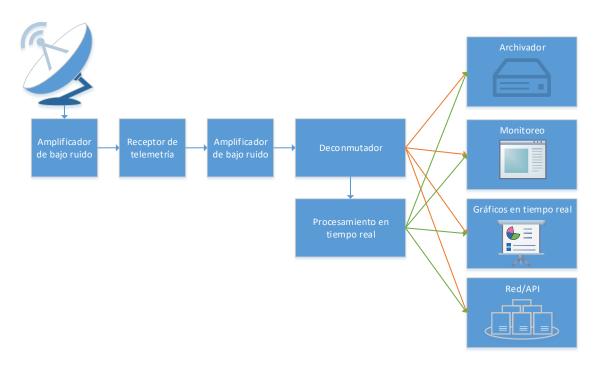

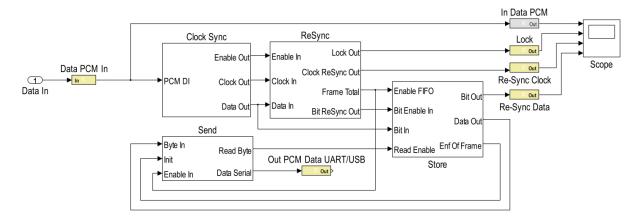

Figura 4. Diagrama en bloques de un Puesto de Tierra

La salida del "Encoder" principal es filtrada y enviada para ser transmitida vía un transmisor de radiofrecuencia, cable coaxil, línea telefónica, etc. El filtrado suaviza la señal digital, es decir, elimina los abruptos cambios entre los estados, y se utiliza para reducir el contenido de frecuencia y por lo tanto el ancho de banda del transmisor necesario. En la estación terrena, Figura 4, el dato recibido es amplificado, y ya que el medio de trasmisión distorsiona la señal filtrada, un sincronizador a nivel de bit (Bit Synchronizer) reconstruye la señal a la serie de pulsos originales. Luego se realiza una de-conmutación (Decom) que reconoce el patrón de sincronismo y paraleliza la señal serie, y además separa la trama PCM en sus valores originales de mediciones (también conocido como parámetros principales) y de datos. El sistema a desarrollar en esta tesis integra el Bit Synchronizer y el Decom en una única unidad de adquisición de bajo costo para luego transferir los datos a la o las computadoras que componen el o los clientes de monitoreo.

### 1.2. HARDWARE DE A BORDO

#### 1.2.1. SENSORES

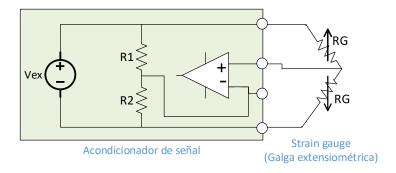

Una amplia variedad de sensores (también conocidos como transductores) se utilizan para medir y adquirir un valor de cierta propiedad física (ver Figura 5). Generalmente el ingeniero de instrumentación selecciona el dispositivo adecuado para satisfacer los requerimientos adecuados para la aplicación de: respuesta, exactitud, tamaño, costo, especificaciones ambientales, etc. Los acondicionadores de señal sirven de interfaz entre los sensores y el sistema de adquisición de datos de a bordo, se acoplan a los sensores analógicos que requieran algún tratamiento de señal como

ser: energía, calibración, amplificación de señal, filtrado, etc. y darle compatibilidad a la próxima etapa del sistema.

Figura 5. Ejemplo de un sensor: Circuito puente básico de galgas extensiométricas

La relación absoluta entre la salida de tensión eléctrica del acondicionador y el valor físico real de la magnitud a medir puede variar con el tiempo, la altitud, presión, temperatura, etc. Por lo tanto, los acondicionadores de señal también incorporan características de calibración para corregir las relaciones mencionadas. Un sistema bajo prueba (DUT – Device Under Test) puede ser sometido a características físicas conocidas y su salida es medida y comparada para determinar y verificar la relación entre el sensor y su salida.

Por ejemplo, estando inmóvil, los flaps de un avión pueden moverse en ángulos conocidos, y se toman mediciones sobre el sensor mismo o en la salida de la electrónica de a bordo. Un gráfico de ángulo vs. salida podrá ser utilizado por el puesto de tierra para el monitoreo de datos en tiempo real, y así evaluar el comportamiento del sistema de adquisición de a bordo.

### 1.2.2. MODULACIÓN

La modulación es la técnica en la que el valor de cada muestra (es decir, la señal modulante) cambia sistemáticamente ciertas características de una señal portadora (por ejemplo, la amplitud (altura) o la frecuencia (tiempo)) (Bryant, 2013). La onda modulada resultante transporta los datos. Inversamente, la eliminación de la señal portadora da como resultado la medición original.

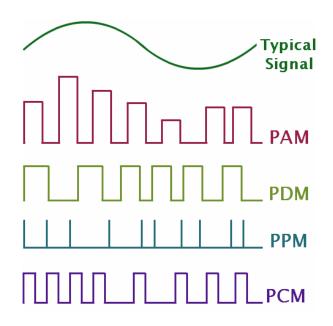

El flujo de datos TDM generado en el esquema básico del multiplexor se lleva a cabo por la señal PCM. También se utilizan otras tres formas de modulación: PDM (modulación de ancho de pulso), PPM (modulación por posición de pulso) y PAM (pulso modulación de amplitud). Las formas de onda resultantes de estas técnicas de modulación de una simple señal de datos analógicos se muestran en la Figura 6.

Figura 6. Diferentes tipos de modulación

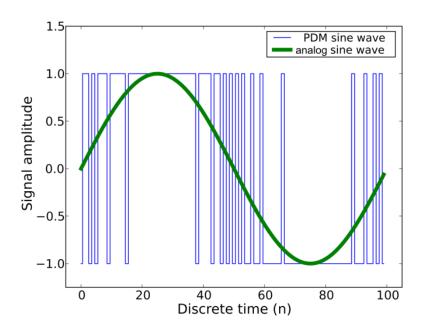

Generalmente los valores de las amplitudes son degradados a causa del ruido, por ello se utilizan flujos de datos multiplexados con un tipo de modulación de pulsos de amplitud constantes. La modulación tipo PDM (Modulación de señal por Densidad de Impulsos) contiene la información en el ancho de pulso, que varía directamente con la amplitud de la señal (Stauth & Sanders, 2008). La Modulación por Posición de Pulso, PPM (Pulse Position Modulation), es el resultado de la diferenciación de la señal PDM y luego rectificada, donde la distancia entre los dos pulsos representa la amplitud muestreada de una onda sinusoidal, con el primer impulso se marca una referencia de tiempo cero. La potencia media de un sistema con PPM es mucho menor que la requerida para una PDM, pero a costa de un mayor ancho de banda.

Figura 7. Ejemplo de señal PDM. Extraído de https://en.wikipedia.org/wiki/Pulse-density\_modulation

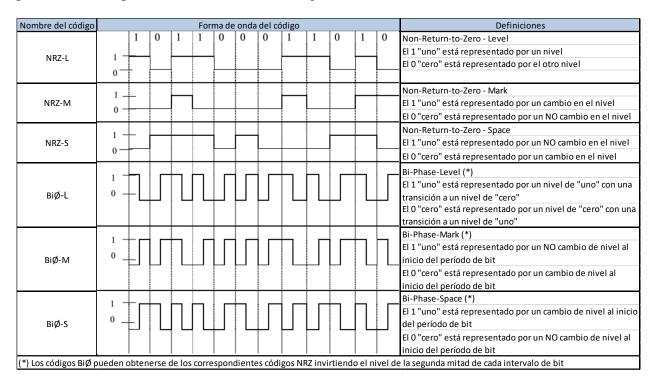

Tanto la PDM como la PPM utilizan pulsos de amplitud constante, pero siguen siendo representaciones analógicas de una señal analógica. En un sistema con PCM, cada pulso es codificado en una representación binaria equivalente antes de la transmisión, esto se denomina "código de línea" <sup>1</sup>. En muchos casos, el dato PCM, no solamente es trasmitido, sino almacenado a bordo también.

En ambos casos, tanto en la grabación como en la transmisión de los datos, se deben establecer que patrones se utilizan para representar una lógica determinada. A través de los años, se han diseñado códigos PCM para representar niveles lógicos, con el fin de lograr el mayor rendimiento para una cierta aplicación (ver detalle en la Figura 8).

Figura 8. Códigos de datos PCM

-

<sup>&</sup>lt;sup>1</sup> En telecomunicaciones, un código en línea o código de línea (modulación en banda base) es un código utilizado en un sistema de comunicación para propósitos de transmisión. Los códigos de línea son frecuentemente utilizados para el transporte digital de datos. Estos códigos consisten en representar la señal digital transportada respecto a su amplitud respecto al tiempo. La representación de la onda se suele realizar mediante un número determinado de pulsos. Estos pulsos representan los "1" (unos) y los "0" (ceros) lógicos. Los tipos más comunes de codificación en línea son el unipolar, polar, bipolar y Manchester.

### 1.2.3. CONMUTACIÓN

Un barrido completo por el multiplexor produce un flujo de datos con palabras que contienen el valor de cada medición, y cada escaneo genera la misma secuencia de palabras, solamente el valor de cada mesurando es capturado, no el nombre de la medición. Si cada dato de la medición es adquirido, no existe manera de distinguirlas entre sí. Por lo tanto, se adiciona una palabra única llamada sincronismo de trama, al principio o al final de cada trama para ser utilizada como referencia en el proceso de de-conmutación de datos donde se extrae cada valor individual (ver Figura 9).

Figura 9. Conmutación básica con sincronismo de trama

Como ejemplo podríamos decir que para caracterizar una vibración determinada en una aeronave requerimos varias muestras por segundo (cientos) a comparación de querer adquirir una temperatura determinada. Teniendo en cuenta el teorema de Nyquist, uno debe muestrear el dato como mínimo el doble de la máxima componente de frecuencia que quiere ser capturada, típicamente se utiliza un muestreo de 5 veces por encima de la máxima frecuencia para estos casos, y se le adiciona un filtro pasabajo para eliminar frecuencias que uno no puede digitalizar precisamente y prevenir el efecto conocido como "aliasing" (ScienceDirect - ELSEVIER, s.f.).

Si tomamos la peor condición de muestrear todo a la máxima tasa, es de esperar que exista una cantidad de residuos apreciables en el espectro de frecuencia de la portadora y la potencia. Por lo tanto, las tasas de muestreo deben variar con respecto al contenido frecuencial y ser un tanto independiente uno de otro, los valores de mediciones que posean diferentes velocidades de adquisición. Esto se puede solucionar con la técnica de super-conmutación (Figura 10) donde el mesurando aparece varias veces en cada trama.

La magnitud del sensor 3 se muestrea 3 veces por cada vuelta del conmutador, es decir, aparece 3 veces por cada trama.

Figura 10. Esquema general de una super-conmutación

El esquema contrario ocurre en la sub-conmutación y datos asíncronos embebidos, donde una posición en el tiempo tiene varios significados.

## 1.2.4. PATRONES DE SINCRONIZACIÓN DE DATOS

La identificación de cada trama se logra a través de la palabra de sincronización, la cual es una secuencia única de unos y ceros. Generalmente, el patrón de sincronismo es una secuencia pseudo-aleatoria que es poco probable que se produzca al azar en los datos adquiridos y típicamente ocupa dos palabras (o más) en el principio de una trama determinada.

El estándar IRIG106 recomienda una lista de patrones de sincronismo para longitudes de 16 hasta 33 bits, ver Tabla 1, donde los primeros tres bits a transmitir deben ser siempre un "1", independientemente si se utiliza una alineación de MSB (Bit Más Significativo - Most Significant Bits) o LSB (Bit Menos Significativo - Least Significant Bit).

Tabla 1. Patrones de sincronismo recomendados por el estándar IRIG106

| Longitud |     |     |     |     | P   | atrones | S   |     |     |     |   |

|----------|-----|-----|-----|-----|-----|---------|-----|-----|-----|-----|---|

| 16       | 111 | 010 | 111 | 001 | 000 | 0       |     |     |     |     |   |

| 17       | 111 | 100 | 110 | 101 | 000 | 00      |     |     |     |     |   |

| 18       | 111 | 100 | 110 | 101 | 000 | 000     |     |     |     |     |   |

| 19       | 111 | 110 | 011 | 001 | 010 | 000     | 0   |     |     |     |   |

| 20       | 111 | 011 | 011 | 110 | 001 | 000     | 00  |     |     |     |   |

| 21       | 111 | 011 | 101 | 001 | 011 | 000     | 000 |     |     |     |   |

| 22       | 111 | 100 | 110 | 110 | 101 | 000     | 000 | 0   |     |     |   |

| 23       | 111 | 101 | 011 | 100 | 110 | 100     | 000 | 00  |     |     |   |

| 24       | 111 | 110 | 101 | 111 | 001 | 100     | 100 | 000 |     |     |   |

| 25       | 111 | 110 | 010 | 110 | 111 | 000     | 100 | 000 | 0   |     |   |

| 26       | 111 | 110 | 100 | 110 | 101 | 100     | 110 | 000 | 00  |     |   |

| 27       | 111 | 110 | 101 | 101 | 001 | 100     | 110 | 000 | 000 |     |   |

| 28       | 111 | 101 | 011 | 110 | 010 | 110     | 011 | 000 | 000 | 0   |   |

| 29       | 111 | 101 | 011 | 110 | 011 | 001     | 101 | 000 | 000 | 00  |   |

| 30       | 111 | 110 | 101 | 111 | 001 | 100     | 110 | 100 | 000 | 000 |   |

| 31       | 111 | 111 | 100 | 110 | 111 | 110     | 101 | 000 | 010 | 000 | 0 |

| 32 | 111 | 111 | 100 | 110 | 101 | 100 | 101 | 000 | 010 | 000 | 00  |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 33 | 111 | 110 | 111 | 010 | 011 | 101 | 001 | 010 | 010 | 011 | 000 |

La longitud de la sincronización de trama generalmente es más larga que las palabras de datos para reducir la probabilidad de que los datos reales se igualen a ella. El sincronismo de trama también debe estar en proporción con el número de palabras de la trama (por lo general, ocupa de 1% a 5% de la trama). El de-commutator es programado para engancharse a este patrón para comenzar la regeneración de los valores de las mediciones originales conmutadas.

#### 1.3. PUESTO DE TIERRA

La creación de una estación terrestre de telemetría incluye:

- ✓ Definir para el sistema de adquisición de datos, las características de los sensores y acondicionadores de señal.

- ✓ Verificar que la estructura de telemetría se adapte a los requisitos de frecuencia de muestreo, así como las limitaciones del hardware de adquisición.

- ✓ La trama de datos se deberá definir hasta el nivel de palabras y bits para poder mostrar los resultados o los datos analizados en tiempo real.

- ✓ Definición de los datos para las palabras adecuadas para gestionar un simulador PCM para la evaluación del sistema.

- ✓ Establecer los datos de calibración para cada sensor (por ejemplo, utilizando base de datos) y de ser necesario crear algoritmos de procesamiento y coeficientes de escalado para convertir parámetros a unidades físicas de ingeniería.

- ✓ Creación de visualizadores para cada tipo de medición, con sus atributos necesarios y unidades físicas.

- ✓ Definir qué datos se almacenan en disco.

El tiempo necesario para configurar y verificar los sistemas de telemetría es significativo dado que los archivos de instalación para el sistema aéreo y terrestre contienen un gran número de datos. Para ello pueden ser útiles el uso de herramientas de auto-configuración o sistema de base de datos.

# 1.3.1. RECONSTRUCCIÓN DE LA TRAMA PCM

En la estación de tierra, la trama PCM, ya sea que ingrese directamente por líneas de cobre o fibra óptica, o que se reciba por una antena y un receptor de telemetría, es reconstruida en sus datos crudos originales (Figura 1).

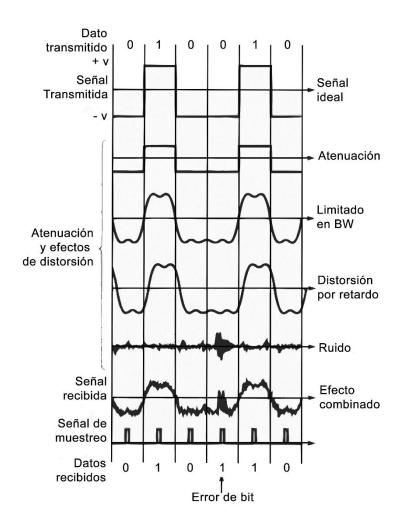

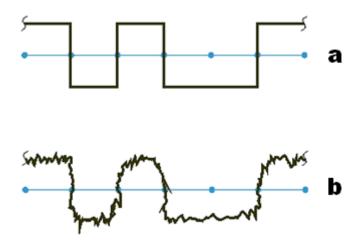

Debido a que el sistema de trasmisión distorsiona la señal (Figura 11), la señal PCM recibida debe ser reconstruida. Antes de ser transmitida, la señal de datos PCM es filtrada para reducir el ancho de banda requerido y asegurando que la potencia se concentre en el espectro que lleva el dato (Dostis).

Figura 11. Efectos en una señal PCM. Extraído de (Halsall, 1995) Figura 2.6, Pág. 32

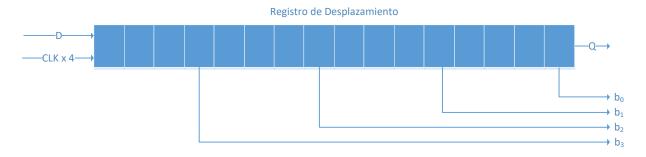

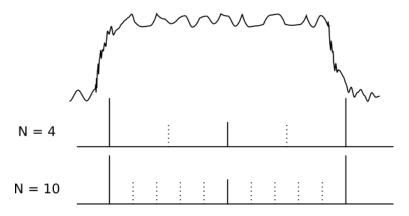

La primera función en el procesamiento de la señal de la adquisición es reconstruir el flujo de datos con un número mínimo de errores en símbolos (en este caso, cada símbolo está representado por un byte). A continuación, a la información reconstruida se le genera una temporización sincrónica, es decir, se reconstruye el "clock" original de la señal PCM. Esta función fundamental, de procesamiento de señal, se denomina sincronización de bits. Un sincronizador de bits (Bit Synchronizer o Bit-Sync) es un dispositivo que establece una serie de pulsos de "clock" que son sincrónicos en una señal entrante ("enganchados" con el patrón de sincronismo).

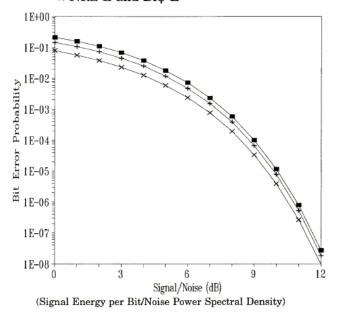

En este desarrollo, la señal que ingresa al Bit-Sync se amplifica e ingresa a un oscilador interno que se engancha con los datos. Cada bit que ingresa al Bit-Sync se reconstruye con un algoritmo

específico (en este trabajo de tesis se explica el método en el Capitulo 3), determina si el nivel de la señal se corresponde con un "0" lógico o un "1" lógico, y su rendimiento (cuan eficaz es la interpretación de bits del Bit-Sync) se obtiene de una curva teórica de "Relación señal ruido vs. Tasa de error de bit", ver en la Figura 12.

■ RNRZ-L

+ NRZ and Bi\u00f3 Mark and Space Codes

× NRZ-L and Bi\u00f4-L

Figura 12. Rendimiento teórico de probabilidad de error de bits de para diversas técnicas en PCM (suponiendo una perfecta sincronización de bits). Extraído de (Telemetry Standars, 2015).

## 1.3.2. SINCRONIZACIÓN DE TRAMAS

Las tramas PCM no solamente deberían ser recibidas en forma contigua, completas y sin errores, además deben ser aisladas del sincronismo, lo cual es una terea es ardua y compleja de por sí debido a la presencia de:

- ✓ Errores de bits: Aparece un "1" donde debería haber un "0", o viceversa.

- ✓ Desplazamientos: Perdidas de un bit o varios bits contiguos, bits no detectados.

- ✓ Secuencias aleatorias de datos: Ruido inherente al sistema.

El operador del puesto de tierra podría elegir el número de tramas válidas antes de aceptar los datos. Esto se podría realizar mediante alguna especificación en la detección del sincronismo en la trama. En este trabajo se utiliza solamente una trama, ya que el sincronismo es chequeado constantemente en la recepción. En algunas aplicaciones específicas, generalmente científicas, esto es una tarea crítica y se debe contemplar no recibir tramas erróneas, y si fuera así, corregirla para obtener todas las tramas válidas. Para esto, se puede considerar cuatro modos operacionales, ver Figura 13.

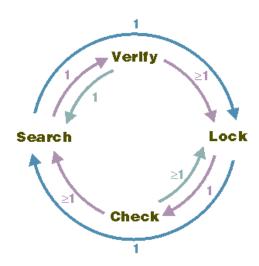

Figura 13. Estados en la sincronización de tramas (los números en violeta indican la cantidad de tramas válidas que deben estar presentes para poder pasar al próximo estado, los celestes indican números de tramas invalidas)

- Search (Búsqueda): El sincronizador rastrea algún posible patrón de sincronismo.

- Verify (Verificación): Una vez que se detecta un tentativo patrón, se fija una ventana en un tiempo fijo y se predice la re-ocurrencia del patrón de sincronismo. Si el patrón vuelve a aparecer en la ventana preestablecida, para un número de dado de tramas determinado, el sincronizado avanza al estado "Lock".

- Lock (Enganche): Una vez que la sincronización se establece, podrán ser identificados los diferentes canales que contienen los valores de las mediciones.

- Check (Chequeo): Si luego de un enganche, no se encuentra un patrón de sincronismo, que queda en este estado.

Las condiciones para pasar de un estado a otro se definen en:

- "Search" to "Lock" (de búsqueda a enganche): Debe ser detectado un número consecutivo de patrones válidos de sincronismo en el flujo de datos antes de avanzar en el Deconmutador. Cuando se detecta el primer patrón válido de sincronismo de trama, se cambia desde el estado "Search" al modo "Verify", y se mantiene en dicho estado hasta que se detecta el segundo patrón válido de sincronismo. Si un tercer patrón de sincronismo es válido, se avanza desde "Verify" a "Lock", si esto no sucede se regresa al estado de "Search". Un emparejamiento del 100% al patrón programado puede no suceder siempre, es por dicho motivo, que el Deconmutador puede tener opciones de configuración para permitirse pasar al próximo estado.

- "Lock" to "Search" (de enganche a búsqueda): Debe ser detectado un número consecutivo de patrones inválidos de sincronismo en el flujo de datos antes de avanzar en el Deconmutador al estado "Search". Cuando se detecta el primer patrón inválido de

sincronismo de trama, se avanza desde el modo "Lock" al modo "Check", y queda en el modo "Check" mencionado cuando se detecta el segundo patrón invalido de sincronismo. Si un tercer patrón de sincronismo es inválido, se avanza a "Search", sino, regresa al estado "Lock".

### Otras características del Bit-Sync son:

- Sync Pattern Bit Errors (errores de bit en el patrón de sincronismo): Se calcula el número

de bits correctos para determinar si un patrón de sincronismo de trama es válido o no. Por

ejemplo, si el patrón de sincronismo posee una longitud de 32 bits, y el "Sync Pattern Bit

Errors" se configura en 4, se buscará que al menos 28 bits estén correctos dentro de dicho

patrón.

- Bit Aperture (apertura de bit): Se puede habilitar o deshabilitar el desplazamiento de bits (bit slip) en el patrón de sincronismo de trama. Por ejemplo, si dicha constante se configura en "1", se permite que el patrón de la trama de sincronismo llegue un bit "antes" o 1 bit "después" y sigue siendo válido.

### 1.3.3. DE-CONMUTACIÓN

Después de la sincronización de trama, los canales individuales que contienen los valores de las mediciones son identificados de acuerdo a la posición en dicha trama. Existen diferentes arquitecturas de hardware/software que contienen las definiciones y relaciones de los datos. Por ejemplo, se puede anexar una etiqueta única a cada mensurando de la trama cruda o palabra de datos, y que puede denominarse arquitectura de flujo de datos, y esta etiqueta mantiene el valor de la medición para luego ser convertido en unidades físicas o ser procesado. Otra arquitectura común es reacomodar los datos en un nuevo formato o estructura que sea más apropiada para el tratamiento de señales.

Las aplicaciones como el monitoreo de cohetes sonda o ensayos en vehículos aéreos requieren una visualización de múltiples parámetros en simultáneo tanto remotos como locales. Por lo tanto, se pueden unificar todos los datos en una única gran estructura y así poder contemplar todos los valores de mediciones posibles en la visualización.

Para poder obtener una rápida respuesta, el deconmutador puede contener definiciones de tipos de datos ya integradas al hardware. El estándar IRIG-106 soporta 16 formatos. En este caso se requieren algunos pocos formatos comunes para aplicaciones de lanzamiento de cohetes sonda y vuelos de aeronaves, pero las velocidades de muestreo son relativamente altas, por este motivo se emplea un conjunto de hardware dedicado y software particular. En otras aplicaciones, por ejemplo, en el monitoreo de satélites, si bien se utilizan ciento de tipos de formatos de datos, las

tasas de muestreo son relativamente bajas, y mayormente se utiliza software para el procesamiento de datos.

## 1.3.4. SIMULACIÓN Y CODIFICACIÓN

Es altamente deseable contar con un simulador de datos PCM para producir datos PCM que permita verificar y ensayar el sistema en general. Existen varios tipos de simuladores con deferentes características y su salida PCM es compatible con el estándar IRIG-106. Los mesurandos contenidos en la trama pueden ser estáticos o variables conocidos para poder cotejar los resultados y evaluar el comportamiento del sistema adquisidor cuando los sistemas sean críticos o de fines científicos.

#### 1.3.5. PROCESAMIENTO EN TIEMPO REAL

Es una característica donde el operador del sistema de tierra puede contemplar un procesamiento en los datos del deconmutador, por ejemplo, una manipulación a nivel de bits, la cual se debe realizar en tiempo real y evitar latencias en el sistema.

#### 1.3.6. GRAFICADORES DE TIEMPO REAL

La visualización en un puesto de tierra es diferente para cada tipo de dato. Por ejemplo, se puede utilizar un tipo de monitoreo de valores para datos alfanuméricos o graficadores en tiempo real para datos procesados, o escenarios en tres dimensiones para evaluaciones de trayectorias.

La utilización de redes e intranet amplían el dominio del monitoreo más allá de la consola del operador, de modo que cada usuario visualiza los datos de interés de manera precisa e independiente de los demás.

### 1.3.7. GESTIÓN DE ARCHIVOS

El almacenamiento de los datos telemétricos capturados se utiliza para post-procesamiento de la información y para evaluar la optimización de algoritmos u otras cuestiones de la aplicación. Típicamente se almacena el dato crudo, el cual es el más cercano a la señal recibida, también se almacena el dato de-conmutado y su estructura cruda. Estos datos son almacenados en discos rígidos o memorias de estado sólido. Se puede tener la opción para almacenar toda la información PCM o solamente la de interés, aunque en este trabajo se almacenarán ambas.

# 1.3.8. DISTRIBUCIÓN DE DATOS

Las arquitecturas basadas en redes de computadoras tipo LAN (Local Area Network – Red de área local) permiten la distribución de los datos en tiempo real hacia estaciones de trabajo

(computadoras), donde se visualiza, analiza y almacena el flujo de información de manera individual.

Los grandes sistemas de puerto de tierra a menudo responden a características particulares (de hardware y de software) para poder distribuir datos en tiempo real. Los clientes o nodos conectados a una red deben estar diseñados específicamente para no solapar los datos cuando el sistema es diseñado para altas tasas de muestreo. Para evitar este problema, en ciertos casos, se recurre a técnicas de compresión de datos, el cual reduce la cantidad de información notablemente en la red, aunque en aplicaciones científicas esto podría implicar tener un error y demoras considerables en el tratamiento de la información. En este trabajo, dada las características y requerimientos proyectuales, fue sumamente necesario diseñar el sistema entero sin pérdida de datos y sin compresión.

## 1.4. FIN DEL CAPÍTULO

A partir de esta información teórica, se pasará a estudiar la tecnología FPGA para luego implementar el adquisidor. Se pretende que el adquisidor forme parte de un puerto de tierra completo aplicando lo mencionado en este capítulo, tanto en hardware como en software.

# CAPÍTULO 2 - TECNOLOGÍA FPGA

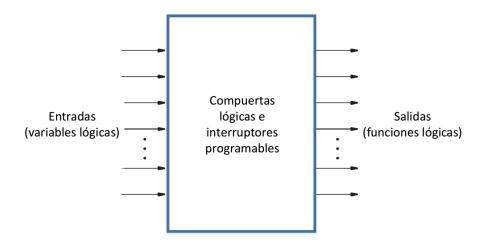

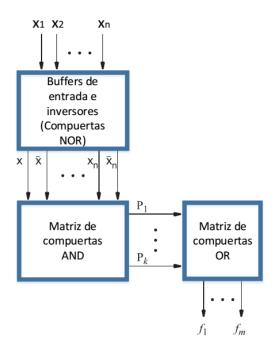

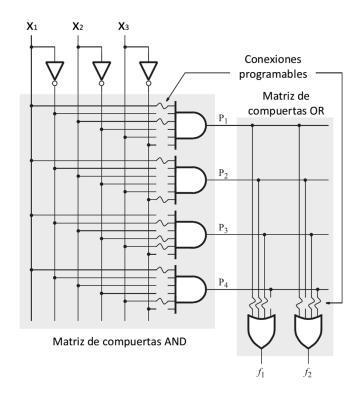

En este capítulo se introduce a los dispositivos lógicos programables y su evolución hasta los FPGA (siglas en inglés, *Field Programmable Gate Arrays*) que es nuestro caso de estudio para el diseño e implementación, analizando su arquitectura, tecnología, sus formas de programación<sup>2</sup> e implementación y las diferentes áreas en donde se puede aplicar esta tecnología.

Las FPGA son dispositivos semiconductores que contienen bloques interconectados en forma matricial programables denominados CLBs (Bloques Lógicos Programables - Configurable Logic Blocks). Estas FPGAs pueden ser programadas y re-programadas para cumplir con una aplicación deseada o requerimientos específicos, esta característica denota la diferencia con las ASICs (Circuitos Integrados para Aplicaciones Específicas), las cuales son fabricadas concretamente para un único diseño o única tarea. Si bien existen FPGA con memoria OTP (programables una única vez), las dominantes son las basadas en memoria del tipo SRAM donde pueden ser re-programadas a medida que evoluciona el diseño.

Una particularidad de las FPGAs es que son dispositivos multinivel programables de propósito general ya que integran una gran cantidad de dispositivos lógicos programables en un solo chip. El tamaño y velocidad de los FPGA es comparable a los ASICs, pero los FPGA son más flexibles, su ciclo de diseño es más corto y los recursos necesarios generan menores gastos. La adopción de chips FPGA en la industria ha sido impulsada por el hecho de que los FPGAs combinan lo mejor de los ASICs y de los sistemas basados en procesadores.

Debido a su naturaleza programable, las FPGAs son un complemento ideal para muchos mercados diferentes. Una firma líder de estos dispositivos es Xilinx (Xilinx, 2020), la cual proporciona soluciones completas que consisten en dispositivos FPGA, software avanzado y núcleos integradores de procesamiento (en inglés, IP cores), listas para su uso en aplicaciones (Xilinx Inc., s.f.), tales como:

- ✓ Defensa y entorno Aeroespacial: Las FPGAs tolerantes a la radiación en conjunto con diseño de propiedad intelectual para el procesamiento de imágenes, la generación de formas de onda, y la reconfiguración parcial de sistemas de radiocomunicaciones del tipo SDR (del inglés Software Defined Radio),

- ✓ Prototipos de ASICs: EL desarrollo de prototipos de ASICs con FPGAs permite el modelado rápido y preciso y la verificación de software embebido para SoC (sistemas en chip system on chip).

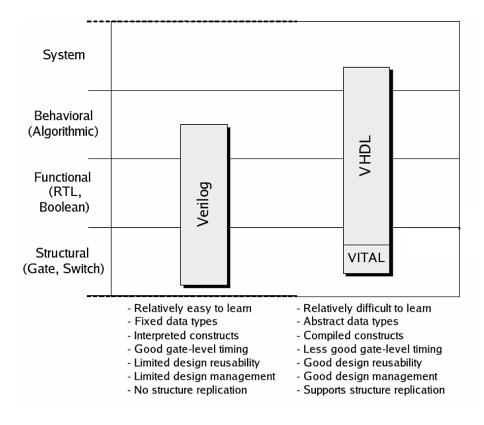

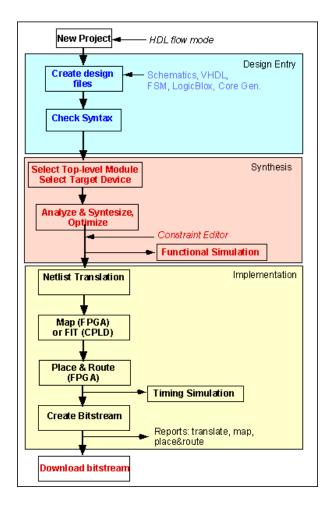

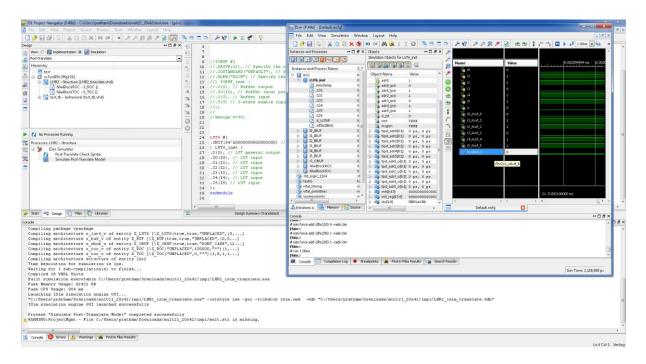

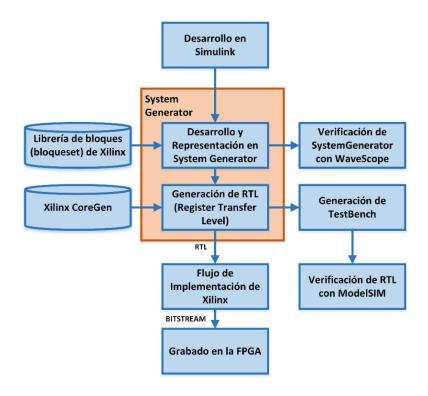

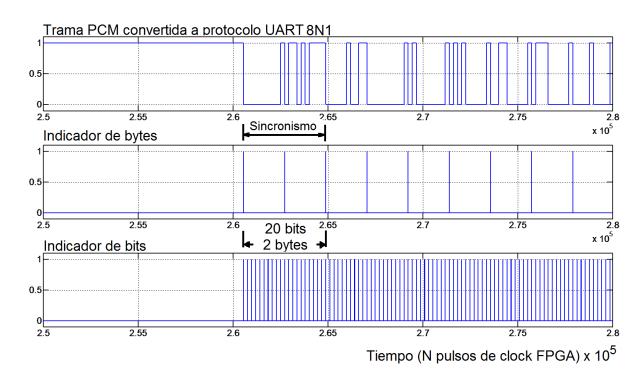

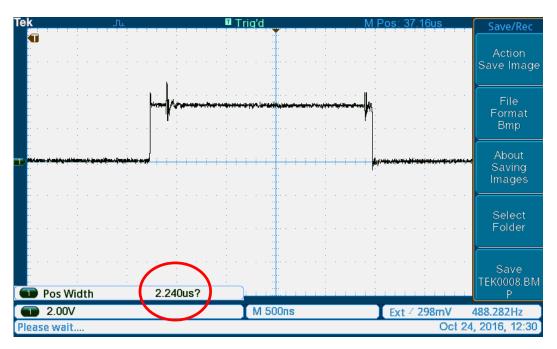

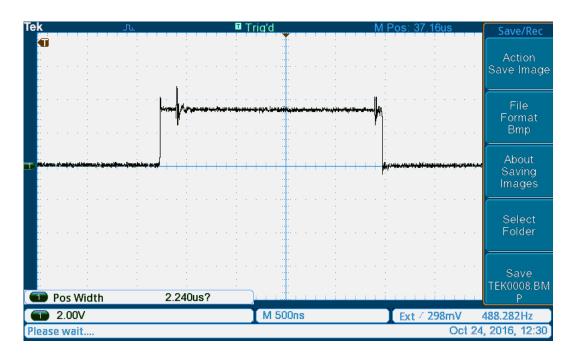

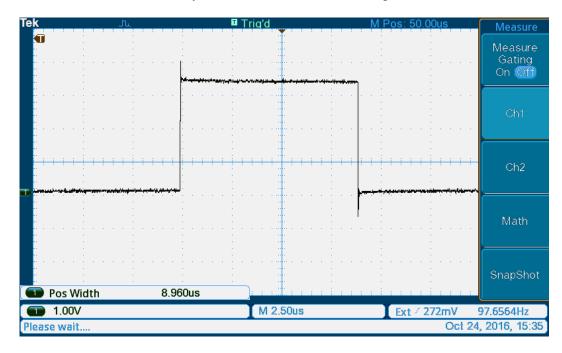

-